# 42V<sub>IN</sub> Micropower No-Opto

# Isolated Flyback Converter with 65V/1.4A Switch

Parameters Subject to Change Without Notice

### **DESCRIPTION**

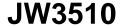

The JW<sup>®</sup>3510 is a micropower isolated flyback converter. By sampling the isolated output voltage directly from the primary-side flyback waveform, the part requires no third winding or opto-isolator for regulation. The output voltage can be programmed with a single external resistor. Besides, internal compensation and soft-start further reduce external component count.

The JW3510 operates with an input voltage range of 3.0V to 42V and can deliver up to 6W of isolated output power. The primary-side can deliver 1.4A peak current with an internal integrated 65V N-Channel DMOS power switch. The JW3510 is designed with boundary mode, discontinuous mode and burst mode operation at different load to improve load regulation and maintain high efficiency while minimizing the output voltage ripple.

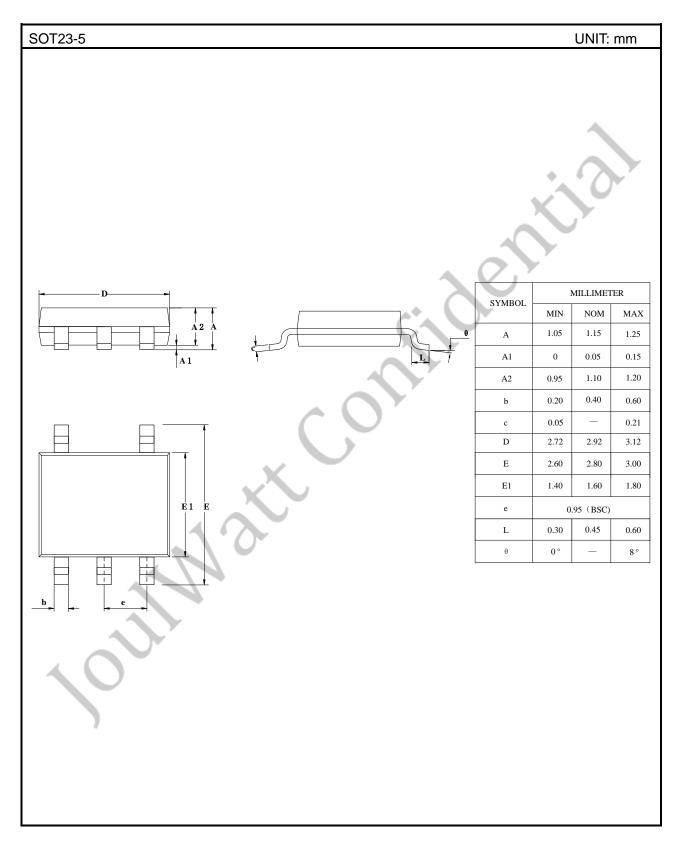

JW3510 is available in the SOT23-5 package. The high level of integration results in a simple to use, low component count, and high efficiency application solution for isolated power delivery.

Company's Logo is Protected, "JW" and "JOULWATT" are Registered Trademarks of JoulWatt technology Inc.

# **FEATURES**

- 3.0V to 42V Operating Input Range

- 1.4A, 65V Internal DMOS Power Switch

- Up to 430KHz Operating Frequency

- Low Quiescent Current

- Boundary Mode Operation at Heavy Load

- Burst Mode Operation at Light Load

- V<sub>OUT</sub> Set with a Single External Resistor

- Minimum Load<0.5% (Typ) of Full Output</li>

- No Transformer Third Winding or Opto-Isolator Required for Regulation

- Internal Compensation and Soft-Start

- Input under voltage lockout

- Output Short-Circuit Protection

- Thermal Protection

- SOT23-5 Package

# **APPLICATIONS**

- Isolated Telecom, Automotive, Industrial, Housekeeping Power Supplies

- Isolated Auxiliary Power Supplies

- Wide Input Voltage Range Micropower system.

# TYPICAK APPLICATION

# ORDER INFORMATION

| DEVICE <sup>1)</sup> | PACKAGE | TOP MARKING <sup>2)</sup> |

|----------------------|---------|---------------------------|

| JW3510SOTA#TRPBF     | COT22 F | JWKB□                     |

|                      | SOT23-5 | YW□□□                     |

#### Notes:

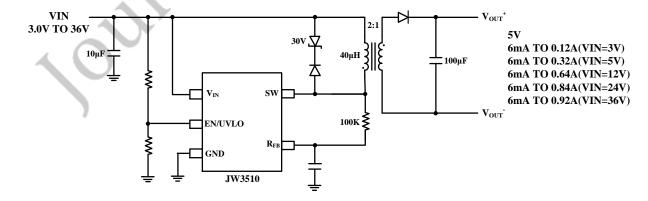

## PIN CONFIGURATION

# ABSOLUTE MAXIMUM RATING1)

| SW                                 | 65V                                      |

|------------------------------------|------------------------------------------|

| V <sub>IN</sub>                    | 42V                                      |

| EN/UVLO                            | V <sub>IN</sub>                          |

| R <sub>FB</sub>                    | V <sub>IN</sub> -0.5V to V <sub>IN</sub> |

| Current into R <sub>FB</sub>       |                                          |

| Junction temperature <sup>2)</sup> | 150°C                                    |

| Storage temperature                | 65°C to +150°C                           |

# **RECOMMENDED OPERATION CONDITIONS**

| Operating Junction Temp (T <sub>J</sub> ) <sup>2)</sup> | -40°C to 125°C |

|---------------------------------------------------------|----------------|

| SW pin                                                  | 0V to 63V      |

| V <sub>INI</sub> nin                                    | 3V to 40V      |

# THERMAL RESISTANCE<sup>3)</sup> $heta_{JA} heta_{JC}$

#### Note:

- 1) Exceeding these ratings may damage the device.

- 2) The JW3510 guarantees robust performance from -40°C to 150°C junction temperature. The junction temperature range specification is assured by design, characterization and correlation with statistical process controls.

- 3) Measured on JEDEC51-7, 4-layer PCB.

# **ELECTRICAL CHARACTERISTICS**

| $T_A$ =25 $^{\circ}C$ , unless otherwise noted        |                       |                           |      |      |      |      |

|-------------------------------------------------------|-----------------------|---------------------------|------|------|------|------|

| PARAMETER                                             | SYMBOL                | <b>TEST CONDITIONS</b>    | MIN  | TYP  | MAX  | UNIT |

| Input Voltage Range                                   | V <sub>IN</sub>       |                           | 3.0  |      | 42   | ٧    |

| EN/UVLO Threshold                                     |                       | Rising                    | 1.1  | 1.2  | 1.3  | V    |

|                                                       |                       | Falling                   | 1.0  | 1.1  | 1.2  | V    |

| V <sub>IN</sub> Quiescent Current                     |                       | EN=0V                     |      | 0.1  | 0.6  | μA   |

|                                                       | ΙQ                    | Sleep Mode (Switch Off)   | 150  | 170  | 250  | μΑ   |

|                                                       |                       | Active Mode (Switch On)   | 650  | 780  | 900  | μA   |

| Thermal Shutdown                                      | T <sub>SDN</sub>      | Shutdown temperature      |      | 140  |      | • °C |

| Thermal Shuldown                                      |                       | Hysteresis                |      | 10   | )    |      |

| Minimum Switching Frequency                           | f <sub>MIN</sub>      |                           | 4    | 7    | 10   | kHz  |

| Minimum Switch-On Time                                | t <sub>ON(MIN)</sub>  | -                         | 300  | 350  | 400  | ns   |

| Minimum Switch-Off Time 4)                            | t <sub>OFF(MIN)</sub> |                           |      |      | 800  | ns   |

| Maximum SW Current Limit                              | I <sub>SW(MAX)</sub>  | CA                        | 1.20 | 1.40 | 1.60 | Α    |

| Minimum SW Current Limit                              | I <sub>SW(MIN)</sub>  |                           | 0.30 | 0.35 | 0.40 | Α    |

| Switch On-Resistance                                  | R <sub>DS(ON)</sub>   | $I_{SW} = 500 \text{mA}$  |      | 0.5  | 0.6  | Ω    |

| R <sub>FB</sub> Regulation Current                    |                       |                           | 95   | 100  | 105  | μΑ   |

| R <sub>FB</sub> Regulation Current Line<br>Regulation | I <sub>RFB</sub>      | $3.0V \le V_{IN} \le 42V$ |      |      | 0.1  | %/V  |

### Note:

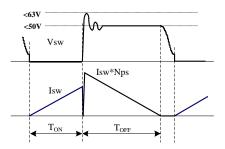

**<sup>4)</sup>** The conduction time of secondary diode, T<sub>OFF</sub>, should be longer than 800ns when SW current is minimum (0.3A). Refer to Figure 1.

# **PIN FUNCTIONS**

| Pin# | Name            | Description                                                                              |

|------|-----------------|------------------------------------------------------------------------------------------|

| 1    |                 | Enable/Under voltage Lockout. The EN/UVLO pin is used to enable the                      |

|      | EN/UVLO         | JW3510. Pull the pin below 1.1V to shut down the JW3510. This pin also                   |

|      |                 | can be used to program a V <sub>IN</sub> under voltage lockout threshold using a         |

|      |                 | external resistor divider from V <sub>IN</sub> to ground.                                |

| 2    | GND             | Ground. Tie this pin directly to local ground plane.                                     |

| 3    | $R_{FB}$        | Input Pin for External Feedback Resistor. Connect a resistor from this pin               |

|      |                 | to the transformer primary SW pin. The ratio of the R <sub>FB</sub> resistor to an       |

|      |                 | internal 10k resistor, times a trimmed 1V reference voltage, determines                  |

|      |                 | the output voltage (plus the effect of any non-unity transformer turns ratio).           |

|      |                 | Minimize trace area at this pin.                                                         |

|      |                 | Collector Node of the Output Switch. This pin has large currents flowing                 |

| 4    | SW              | through it. Drain of the 65V internal DMOS Power Switch. Minimize trace                  |

|      |                 | area at this pin to reduce EMI and voltage spikes.                                       |

| 5    | V <sub>IN</sub> | Input Voltage. The V <sub>IN</sub> pin supplies current to internal circuitry and serves |

|      |                 | as a reference voltage for the feedback circuitry connected to the R <sub>FB</sub> pin.  |

|      |                 | Locally bypass this pin to ground with a capacitor.                                      |

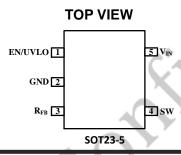

# **FUNCTIONAL BLOCK DIAGRAM**

### FEATURE DESTRIPTION

The JW3510 is a current mode switching regulator IC designed for the isolated flyback topology. It samples the isolated output voltage through the primary-side flyback pulse waveform, so that neither opto-isolator nor extra transformer winding is required for regulation. In this manner, it overcomes the deficiencies of opto-isolator, such as wasting output power, increasing extra components, limiting dynamic response, nonlinearity, unit-to-unit variation and aging over lifetime. Circuit employing extra transformer windings also exhibit deficiencies, as using an extra winding adds to the transformer's physical size and cost, and dynamic response is often mediocre.

Since the JW3510 operates in either boundary conduction mode or discontinuous conduction mode, the output voltage is always sampled on the SW pin when the secondary current is almost zero. This method improves load regulation without the need of external load compensation components.

### **Boundary Conduction Mode**

Boundary conduction mode is a variable frequency, variable peak-current mode switching scheme. The JW3510 operates in boundary conduction mode at heavy load, where the chip turns on primary power switch when the secondary current is zero and the transformer primary current increases until an internally controlled peak current limit. After the power switch turns off, the voltage on the SW pin rises to output voltage multiplied by primary-to-secondary transformer turns ratio plus the input voltage. When the secondary current through the output diode falls to zero, the SW pin voltage falls and rings around V<sub>IN</sub>. A boundary mode detector senses this event and turns the power switch back on.

#### **Discontinuous Conduction Mode**

As the load gets lighter, boundary conduction mode will increase the switching frequency and losses. To avoid this scenario, the JW3510 has an additional internal oscillator which clamps the maximum switching frequency to be less than 430kHz (typ), meanwhile decreases the peak current limit level to a lower value. Once the switching frequency hits the internal frequency clamp, the system starts to delay the switch turn-on and operates in discontinuous conduction mode.

#### **Burst Mode**

Unlike traditional flyback converters, the JW3510 has to turn on and off at least for a minimum amount of time and with a minimum frequency to allow accurate sampling of the output voltage. The inherent minimum switch current limit and minimum switch-off time are necessary to guarantee the correct operation of specific applications.

As the load gets very light, the JW3510 starts to fold back the switching frequency while keeping the minimum switch current limit. So the load current is able to decrease while still allowing minimum switch-off time for the sample-and-hold error amplifier. Meanwhile, the part switches between sleep mode and active mode, thereby reducing the effective quiescent current to improve light load efficiency. In this condition, the JW3510 operates in low ripple Burst Mode. The 10kHz (typ) minimum switching frequency determines how often the output voltage is sampled and also the minimum load requirement.

#### **Output Voltage**

The  $R_{FB}$  resistor as depicted in the Block Diagram is the only external resistor used to program the output voltage. The JW3510 operates similar to

traditional current mode switchers, except in the use of a unique flyback pulse sense circuit and a sample-and-hold error amplifier, which sample and therefore regulate the isolated output voltage from the flyback pulse.

An internal trimmed reference voltage,  $V_{REF}$  1.0V, feeds to the non-inverting input of the sample-and-hold error amplifier. The relatively high gain in the overall loop causes the voltage across  $R_{REF}$  resistor to be nearly equal to  $V_{REF}$ .

The resulting relationship between  $R_{FB}$  and  $V_{REF}$  can be expressed as:

$$\frac{N_{PS} \cdot (V_o + V_F)}{R_{FB}} = \frac{V_{REF}}{R_{REF}} = 100 \,\mu\text{A} \tag{1}$$

Rearrangement of the expression for  $V_{\text{O}}$  in the Output Voltage section yields the starting value for  $R_{\text{FB}}$ :

$$R_{FB} = \frac{N_{PS} \cdot (V_o + V_F)}{100 \,\mu\text{A}} \tag{2}$$

Where,  $N_{PS}$  is the transformer primary-to-secondary turns ratio,  $V_F$  is the output diode forward voltage. Usually, the  $R_{FB}$  is no more than 100K.

## Minimum Load Requirement

In order to sample the isolated output voltage from the primary-side flyback pulse waveform, the JW3510 has to turn on and off at least for a minimum amount of time and with a minimum frequency. The JW3510 delivers a minimum amount of energy even during light load conditions to ensure accurate output voltage information. The minimum energy delivery creates a minimum load requirement, which can be approximately estimated as:

$$I_{O(\text{MIN})} = \frac{L_m \cdot I_{SW(\text{MIN})}^2 \cdot f_{\text{MIN}}}{2V_o}$$

(3)

Where,  $L_m$  is the transformer primary inductance,  $I_{SW(MIN)}$  is the minimum switch current limit,  $f_{MIN}$  is the minimum switch frequency.

### **Output Short-Circuit Protection**

When the output is heavily overloaded or shorted, the reflected SW pin waveform rings longer than the internal blanking time. If no protection scheme is applied, after the minimum switch-off time, the excessive ring might falsely trigger the boundary mode detector and turn the power switch back on again before the secondary current falls to zero. The part then runs into continuous conduction mode at maximum switching frequency, and the switch current may run away. To prevent this condition, the JW3510 gradually folds back both maximum switch current limit and switching frequency as the output voltage drops from regulation. This output short protection prevents the switch current from running away and limits the average output diode current.

#### Leakage Inductance and Snubbers

SW pin has voltage spike after the inner MOSFET turning off, causing by leakage inductance, so it is very important to minimize the leakage. The RCD snubber or DZ snubber is recommended to reduce the voltage spike of SW.

As the Figure 1 shows, the reflected output voltage plus V<sub>IN</sub> should be below 50V for practical design. This leaves at least 15V headroom for the voltage spikes caused by the leakage inductance. Generally, the maximum spike voltage should be less than 65V with reasonable margin, such as 5-10% of the device voltage rating, for example 2-5V. A proper design of transformer turns ration and snubber circuit is necessary to achieve these requirements.

Figure 1. the operation waveform of SW

#### **Layout Guidelines**

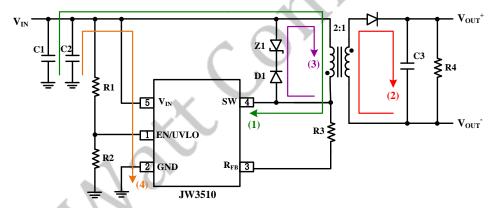

In order to increase the reliability and feasibility of the project it is recommended to adhere to the following guidelines for PCB layout. A typical design schematic is shown in Figure 2.A.

Arrange the components to minimize the loop areas of the switching currents as much as possible. These areas include such loops as the transformer primary winding current loop (1), the secondary output current loop (2), and the primary snubber loop (3).

- Place a decoupling ceramic capacitor from V<sub>IN</sub> to GND close to the IC for adequate filtering.

- In order to avoid the coupling of switching noise, it is strongly recommended that the R<sub>FB</sub> pin path should be as far away from the transformer as possible.

- To improve thermal performance increase the copper area connected to GND pins.

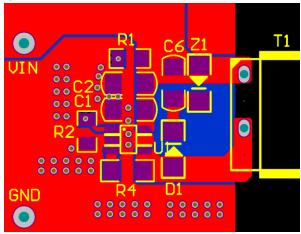

### **Layout Example**

Figure 2.B demonstrates a 5V-5V layout with trade-offs to minimize the loops while effectively

placing components on a double-layer printed circuit board.

Figure 2. A Typical Design Schematic

Figure 2.B Layout Example

# **PACKAGE OUTLINE**

# **IMPORTANT NOTICE**

Joulwatt Technology Inc. reserves the right to make modifications, enhancements, improvements,

corrections or other changes without further notice to this document and any product described herein.

- Any unauthorized redistribution or copy of this document for any purpose is strictly forbidden.

- Joulwatt Technology Inc. does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

Copyright © 2017 JW3510 Incorporated.

All rights are reserved by Joulwatt Technology Inc.