BQ25616, BQ25616J

ZHCSKP6A - JANUARY 2020 -**REVISED FEBRUARY 2022**

# BQ25616/616J 具有电源路径和 1.2A 升压电流的独立单芯 3.0A 降压电池充电器

### 1 特性

- 高效 1.5MHz 同步开关模式降压充电器

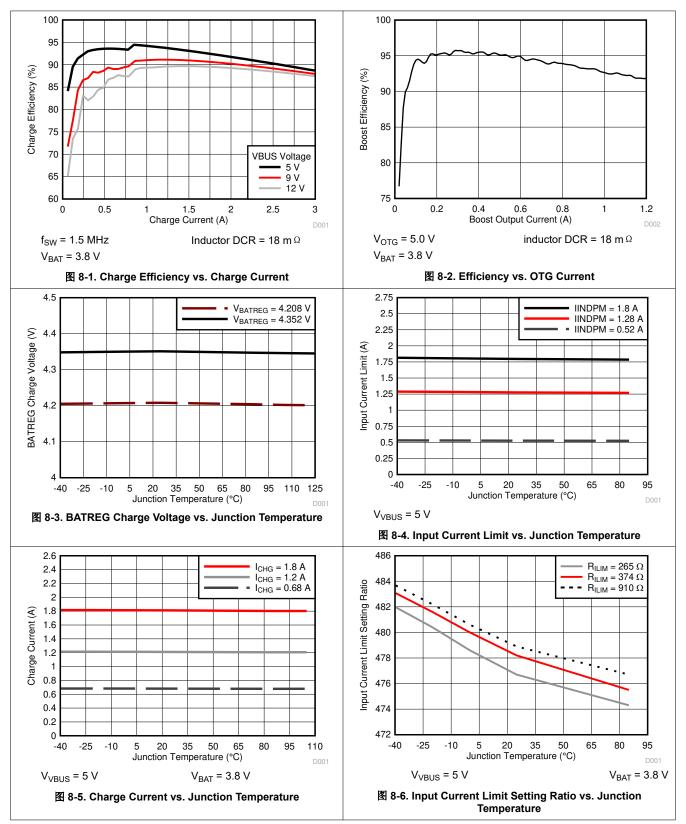

- 在 2A 电流 (5V 输入) 下具有 92% 的充电效率

- ±0.5% 充电电压调节

- 通过 VSET 引脚实现的可调节充电电压支持 4.1V、4.2V 和 4.35 V 电压,稳压精度为 ±0.4%

- 充电电流调节范围为 ±6%

- 输入电流调节范围为 ±7.5%

- 支持 JEITA (BQ25616J) 或热/冷 (BQ25616) 温 度感应曲线

- 10 小时充电安全计时器

- 支持 USB On-The-Go (OTG)

- 具有高达 1.2A 输出的 5V 升压转换器

- 在 1A 输出下具有 92% 的升压效率

- 精确的恒定电流 (CC) 限制

- 高达 500µF 容性负载的软启动

- 用于轻负载运行的 PFM 模式

- 单个输入,支持 USB 输入以及高电压适配器或无线 电源

- 支持 4V 至 13.5V 输入电压范围,绝对最大输入 额定值为 22V

- 130ns 快速关断输入过压保护,可选的外部 OVPFET 可承受高达 30V 的输入电压

- 通过 ILIM 引脚实现可编程输入电流限制 (IINDPM)

- 通过 VINDPM 阈值自动跟踪电池电压,从而实 现最大功率

- 自动检测 USB SDP、CDP、DCP 以及非标准适 配器

- 窄 VDC (NVDC) 电源路径管理

- 无需电池或使用深度放电的电池即可使系统瞬时

- 低 R<sub>DSON</sub> 19.5m Ω BATFET,可更大程度地降低充 电损耗和延长电池运行时间

- 在系统待机时具有 9.5µA 的低电池泄漏电流

- 高集成度包括所有 MOSFET、电流感应和环路补偿

- 安全相关认证:

- 经 IEC 62368-1 CB 认证

### 2 应用

- 电子销售点 (EPOS)

- 无线扬声器

- 工业、医疗 便携式电子产品

### 3 说明

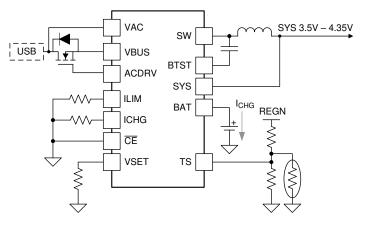

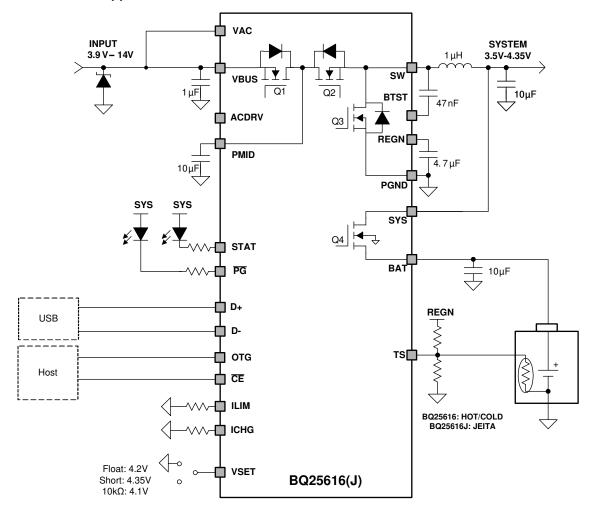

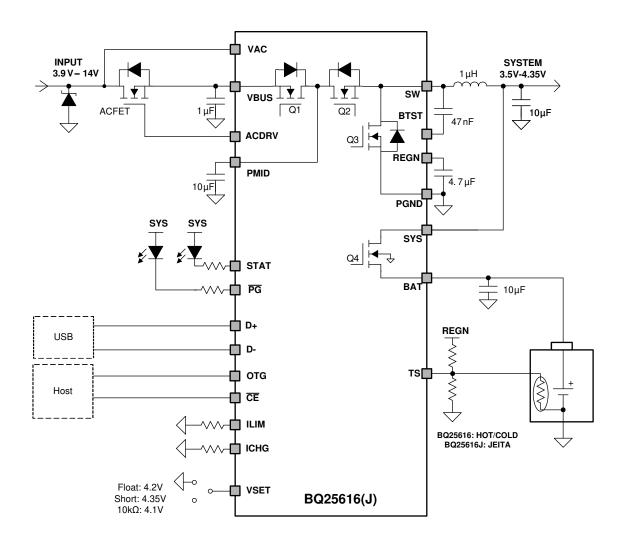

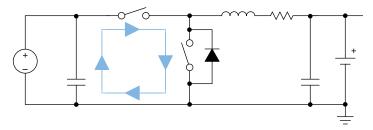

BQ25616/616J 是适用于单节锂离子电池和锂聚合物电 池、高度集成的 3A 开关模式电池充电管理和系统电源 路径管理器件。该解决方案在系统和电池之间高度集成 输入反向阻断 FET(RBFET, Q1)、高侧开关 FET (HSFET, Q2)、低侧开关 FET(LSFET, Q3)以 及电池 FET(BATFET, Q4)。其低阻抗电源路径对 开关模式运行效率进行了优化,缩短了电池充电时间并 延长了放电阶段的电池运行时间。

BQ25616/616J 是适用于锂离子电池和锂聚合物电池、 高度集成的 3A 开关模式电池充电管理和系统电源路径 管理器件。它可为扬声器、工业和医疗便携式设备等各 种应用提供快速充电功能和高输入电压。其低阻抗电源 路径对开关模式运行效率进行了优化,缩短了电池充电 时间并延长了放电阶段的电池运行时间。其输入电压和 电流调节可以为电池提供最大的充电功率。

### 器件信息

| 器件型号         | <b>封装<sup>(1)</sup></b> | 封装尺寸(标称值)       |

|--------------|-------------------------|-----------------|

| BQ25616/616J | WQFN (24)               | 4.00mm × 4.00mm |

如需了解所有可用封装,请参阅数据表末尾的可订购产品附 录。

简化版应用

### **Table of Contents**

| 1 特性                                 | 1 | 9.4 Device Functional Modes             | 28 |

|--------------------------------------|---|-----------------------------------------|----|

| ,,<br>2 应用                           |   | 10 Application and Implementation       | 29 |

| - <i>二, 1</i>                        |   | 10.1 Application Information            | 29 |

| 4 Revision History                   |   | 10.2 Typical Applications               |    |

| 5 说明(续)                              |   | 11 Power Supply Recommendations         | 37 |

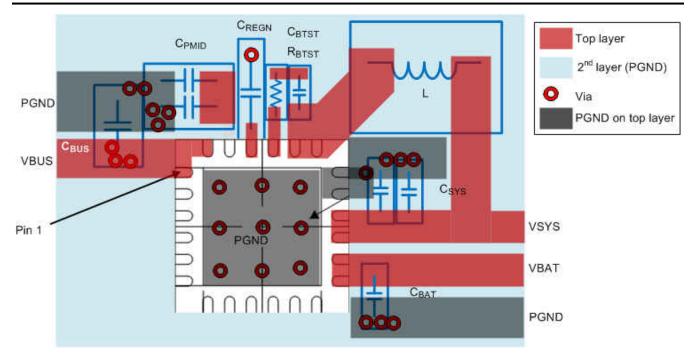

| 6 Device Comparison Table            |   | 12 Layout                               | 38 |

| 7 Pin Configuration and Functions    |   | 12.1 Layout Guidelines                  | 38 |

| 8 Specifications                     |   | 12.2 Layout Example                     | 38 |

| 8.1 Absolute Maximum Ratings         |   | 13 Device and Documentation Support     | 40 |

| 8.2 ESD Ratings                      |   | 13.1 Device Support                     | 40 |

| 8.3 Recommended Operating Conditions |   | 13.2 Documentation Support              | 40 |

| 8.4 Thermal Information              |   | 13.3 接收文档更新通知                           | 40 |

| 8.5 Electrical Characteristics       |   | 13.4 支持资源                               | 40 |

| 8.6 Timing Requirements              |   | 13.5 Trademarks                         | 40 |

| 8.7 Typical Characteristics          |   | 13.6 Electrostatic Discharge Caution    | 40 |

| 9 Detailed Description               |   | 13.7 术语表                                | 40 |

| 9.1 Overview                         |   | 14 Mechanical, Packaging, and Orderable |    |

| 9.2 Functional Block Diagram         |   | Information                             | 41 |

| 9.3 Feature Description              |   |                                         |    |

| •                                    |   |                                         |    |

4 Revision History 注:以前版本的页码可能与当前版本的页码不同

| С | hanges from Revision * (January 2020) to Revision A (February 2022)                               | Page                 |

|---|---------------------------------------------------------------------------------------------------|----------------------|

| • | 将"特性"中的 20 小时充电安全计时器更改为 10 小时充电安全计时器                                                              | 1                    |

| • | 添加了"安全相关认证:经 IEC 62368-1 CB 认证                                                                    | 1                    |

| • | Changed charge safety timer accuracy from 20 hr to 10 hr for BQ25616/J in the Device Comparison   | Table <mark>4</mark> |

| • | Deleted deglitch time and added charge voltage limit in the Device Comparison Table               | 4                    |

| • | Changes TS and VAC pin descriptions in 表 7-1                                                      | <mark>5</mark>       |

| • | Changed voltage, BAT, SYS (converter not switching) MAX value from 17 V to 7 V in 节 8.1           | <mark>7</mark>       |

| • | Added CHARGE OVERCURRENT COMPARATOR (CYCLE-BY-CYCLE) in # 8.5                                     | 8                    |

| • | Deleted V <sub>BST_BAT</sub> and added V <sub>BATLOWV_OTG</sub> in 节 8.5                          | 8                    |

| • |                                                                                                   |                      |

| • | Deleted I <sub>BST OCP Q1</sub> in 节 8.5                                                          | 8                    |

|   | Deleted accuracy from t <sub>TOP OFF</sub> and CHG_TIMER = 20hr from t <sub>SAFETY</sub> in 节 8.6 |                      |

| • | Changed t <sub>SAFETY</sub> MIN/TYP/MAX values in 节 8.6                                           | 13                   |

| • | Deleted V <sub>BATREG</sub> = 4.4 V curve from 图 8-3                                              | 14                   |

| • | Changed safety timer from 20 hours to 10 hours in 表 9-4                                           | <mark>23</mark>      |

|   | Changed T2 from 20 to 10 in 图 9-6                                                                 |                      |

|   | Changed 节 9.3.9.5.3                                                                               |                      |

|   |                                                                                                   |                      |

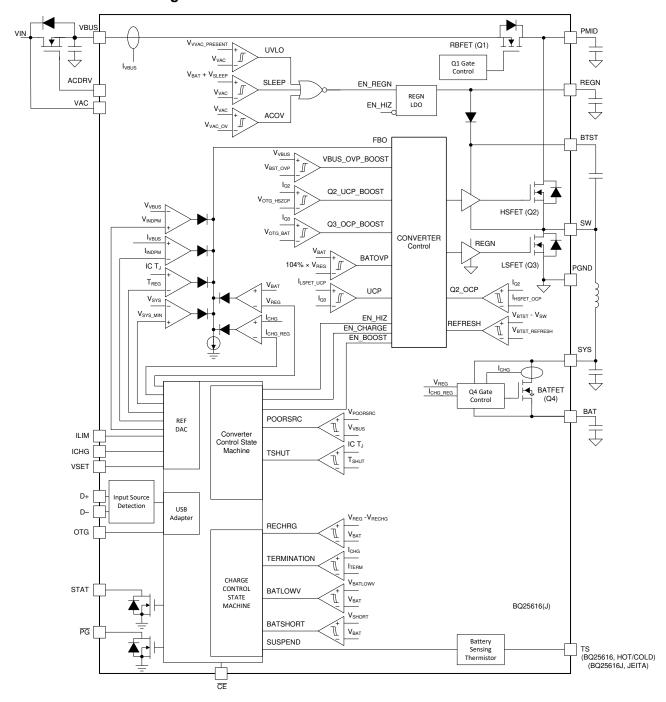

### 5 说明(续)

该解决方案在系统和电池之间高度集成输入反向阻断 FET(RBFET,Q1)、高侧开关 FET(HSFET,Q2)、低侧开关 FET(LSFET,Q3)以及电池 FET(BATFET、Q4)。它还集成了自举二极管以进行高侧栅极驱动,从而简化系统设计。硬件设置和状态报告为充电解决方案提供了简单的配置。

该器件支持多种输入源,包括标准 USB 主机端口、USB 充电端口、兼容 USB 的高电压适配器和无线电源。该器件符合 USB 2.0 和 USB 3.0 电源规格,具有输入电流和电压调节功能。该器件根据内置 USB 检测通过 D+/D- 引脚设置默认输入电流限值。当器件内置 USB 接口确定输入适配器未知时,器件的输入电流限值是通过 ILIM 引脚设置电阻器值来决定的。

该器件通过单个电感器将降压充电器和升压稳压器集成在一个解决方案中。它通过提供 5V 电压和高达 1.2A 的恒定电流限值,符合 USB On-the-Go (OTG) 运行功率额定值规格。

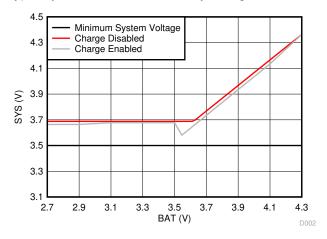

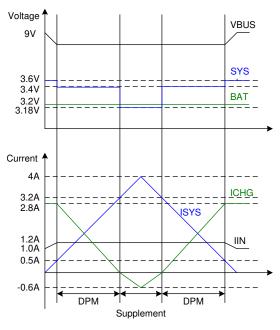

在应用适配器时,电源路径管理将系统电压调节至稍高于电池电压的水平,但不会降至 3.5V 最小系统电压以下。借助于这个特性,即使在电池电量完全耗尽或者电池被拆除时,系统也能保持运行。当达到输入电流限值或电压限值时,电源路径管理会自动减小充电电流。随着系统负载持续增加,电池开始放电,直到满足系统电源需求。该补充模式可防止输入源过载。

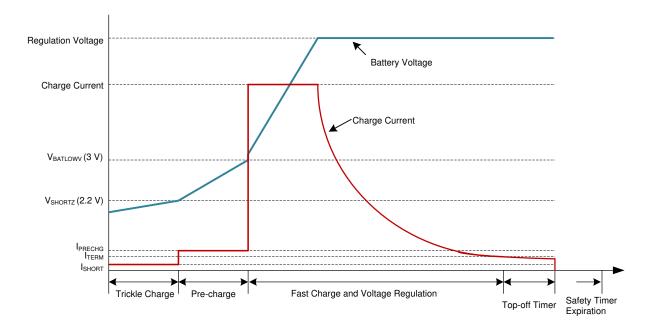

此器件在无需软件控制情况下启动并完成一个充电周期。它感应电池电压并通过三个阶段为电池充电:预充电、恒定电流和恒定电压。在充电周期的末尾,当充电电流低于预设限值并且电池电压高于再充电阈值时,充电器自动终止。如果已完全充电的电池降至再充电阈值以下,则充电器自动启动另一个充电周期。

此充电器提供针对电池充电和系统运行的多种安全特性,其中包括电池负温度系数热敏电阻监视、充电安全性计时器和过压/过流保护。当结温超过 110°C 时,热调节会减小充电电流。STAT 输出报告充电状态和任何故障状况。

# **6 Device Comparison Table**

|                                          | BQ25606            | BQ25616            | BQ25616J           |

|------------------------------------------|--------------------|--------------------|--------------------|

| Quiescent battery current (BAT, SYS, SW) | 58 μA              | 9.5 μΑ             | 9.5 μΑ             |

| VBUS OVP Reaction-time                   | 200 ns             | 130 ns             | 130 ns             |

| Input voltage regulation accuracy        | ±3%                | ±2%                | ±2%                |

| TS profile                               | JEITA              | Hot/Cold           | JEITA              |

| Charge safety timer accuracy             | 10 hr              | 10 hr              | 10 hr              |

| Charge voltage limit                     | 4.2 V/4.35 V/4.4 V | 4.1 V/4.2 V/4.35 V | 4.1 V/4.2 V/4.35 V |

| Battery voltage regulation               | ±0.5%              | ±0.4%              | ±0.4%              |

| ACDRV                                    | No                 | Yes                | Yes                |

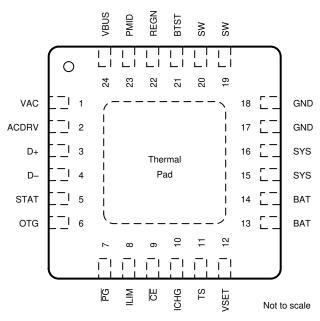

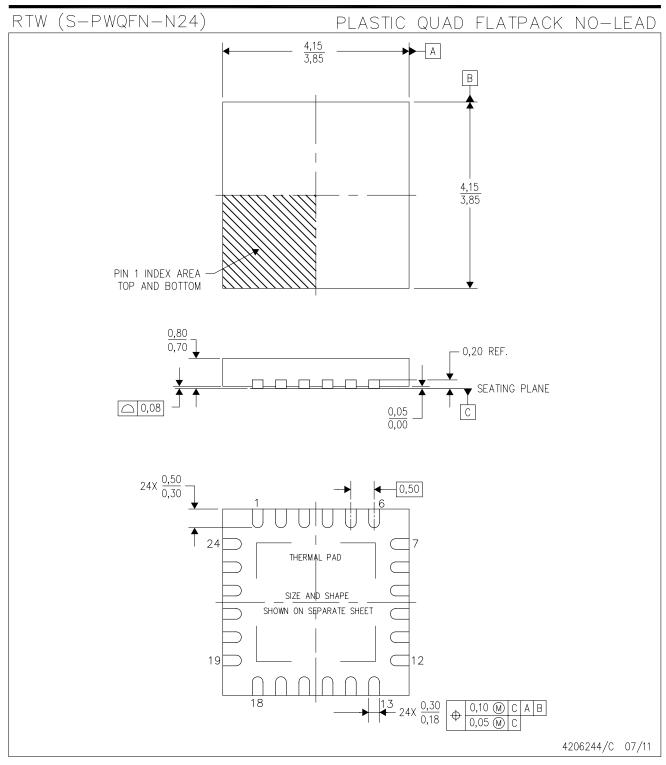

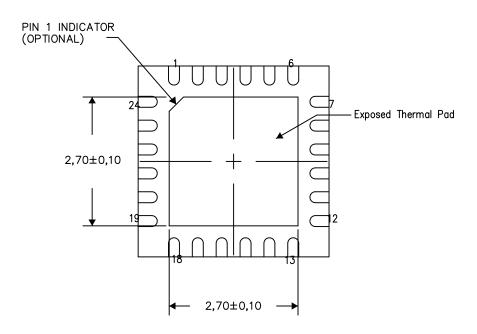

# 7 Pin Configuration and Functions

图 7-1. RTW Package 24-Pin WQFN Top View

表 7-1. Pin Functions

| PIN TYPE <sup>(1)</sup> |          | TVDE(1)                                                                         | DESCRIPTION                                                                                                                                                                                                                                                                                                                            |  |

|-------------------------|----------|---------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                         |          | ITPE                                                                            | DESCRIPTION                                                                                                                                                                                                                                                                                                                            |  |

| ACDRV                   | 2        | AO                                                                              | Charge pump output to drive external N-channel MOSFET (ACFET). It provides 6V voltage above VBUS as gate drive to turn on ACFET when VAC voltage is below ACOV threshold (14.2-V) and above UVLO. Leave ACDRV floating if external OVP is not being used.                                                                              |  |

| BAT                     | 13<br>14 | - P                                                                             | Battery connection point to the positive terminal of the battery pack. The internal current sensing resistor is connected between SYS and BAT. Connect a 10 µF <sup>(2)</sup> closely to the BAT pin.                                                                                                                                  |  |

| BTST                    | 21       | Р                                                                               | PWM high side driver positive supply. Internally, the BTST is connected to the cathode of the boot-strap diode. Connect the 0.047- μ F bootstrap capacitor <sup>(2)</sup> from SW to BTST.                                                                                                                                             |  |

| CE                      | 9        | DI Charge enable pin. When this pin is driven LOW, battery charging is enabled. |                                                                                                                                                                                                                                                                                                                                        |  |

| D+                      | 3        | AIO                                                                             | ositive line of the USB data line pair. D+/D - based USB host/charging port detection. The etection includes data contact detection (DCD), primary and secondary detection in BC1.2 and onstandard adaptors                                                                                                                            |  |

| D -                     | 4        | AIO                                                                             | Negative line of the USB data line pair. D+/D - based USB host/charging port detection. The detection includes data contact detection (DCD), primary and secondary detection in BC1.2 and nonstandard adaptors                                                                                                                         |  |

| GND                     | 17<br>18 | P                                                                               | Power ground and signal ground                                                                                                                                                                                                                                                                                                         |  |

| ICHG                    | 10       | Al                                                                              | ICHG pin sets the charge current limit. A resistor is connected from ICHG pin to ground to set charge current limit as ICHG = K <sub>ICHG</sub> /R <sub>ICHG</sub> . The acceptable range for charge current is 300 mA - 3000 mA.                                                                                                      |  |

| ILIM                    | 8        | Al                                                                              | ILIM sets the input current limit when the input adapter is detected as unknown. Otherwise, the input current limit is set by D+/D $^-$ detection outcome. A resistor is connected from ILIM pin to ground to set the input current limit as IINDPM = $K_{ILIM}/R_{ILIM}$ . The acceptable range for ILIM current is 500 mA - 3200 mA. |  |

| ОТС                     | 6        | DI                                                                              | Boost mode enable pin. When this pin is pulled HIGH, boost mode is enabled. OTG pin cannot be floating.                                                                                                                                                                                                                                |  |

| PG                      | 7        | DO                                                                              | Open drain active low power good indicator. Connect to the pull up rail through 10 k $\Omega$ resistor. LOW indicates a good input if the input voltage is between UVLO and ACOV, above SLEEP mode threshold, and input current limit is above 30 mA.                                                                                  |  |

### 表 7-1. Pin Functions (continued)

| PIN                                                                              |                                                                                                                                                                                                                                                                                                                                             | <b>-</b> > (-)(1)                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME NO.                                                                         |                                                                                                                                                                                                                                                                                                                                             | TYPE <sup>(1)</sup>                                                                                   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| PMID                                                                             | 23                                                                                                                                                                                                                                                                                                                                          | Р                                                                                                     | Connected to the drain of the reverse blocking MOSFET (RBFET) and the drain of HSFET. Place a 10-µF capacitor <sup>(2)</sup> on PMID to GND.                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| REGN                                                                             | 22                                                                                                                                                                                                                                                                                                                                          | Р                                                                                                     | PWM low side driver positive supply output. Internally, REGN is connected to the anode of the poot-strap diode. Connect a 4.7- $\mu$ F (10-V rating) ceramic capacitor <sup>(2)</sup> from REGN to analog GND. The capacitor should be placed close to the IC.                                                                                                                                                                                                                                                                |  |  |  |

| STAT 5 DO Charge in progress: LOW Charge complete or charger in SLEEP mode: HIGH |                                                                                                                                                                                                                                                                                                                                             | Charge in progress: LOW                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| sw                                                                               | 19                                                                                                                                                                                                                                                                                                                                          | P                                                                                                     | Switching node connecting to output inductor. Internally SW is connected to the source of the n-                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| 300                                                                              | 20                                                                                                                                                                                                                                                                                                                                          |                                                                                                       | channel HSFET and the drain of the n-channel LSFET. Connect the 0.047- μ F bootstrap capacitor from SW to BTST.                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| SYS                                                                              | 15                                                                                                                                                                                                                                                                                                                                          | . P                                                                                                   | System output connection point. The internal current sensing resistor is connected between SYS                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 010                                                                              | 16                                                                                                                                                                                                                                                                                                                                          | ] <b>F</b>                                                                                            | and BAT. Connect a 10 µF (min) capacitor <sup>(2)</sup> close to the SYS pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

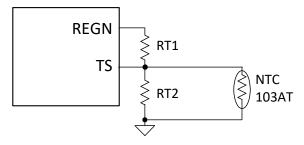

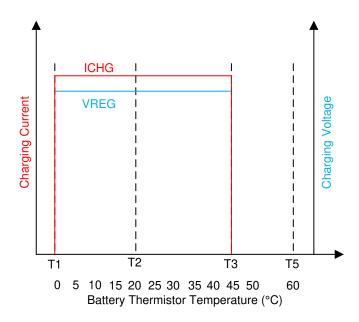

| TS                                                                               | thermistor (NTC). Program temperature window with a resistor divider from REGN to Charge and boost mode suspend when TS pin voltage is out of range. When TS pin is connect a 10-k Ω resistor from REGN to TS and a 10-k Ω resistor from TS to GND. It is recommended to use a 103AT-2 thermistor. BQ25616 supports hot/cold profile and BQ |                                                                                                       | Battery temperature qualification voltage input. Connect a negative temperature coefficient thermistor (NTC). Program temperature window with a resistor divider from REGN to TS to GND. Charge and boost mode suspend when TS pin voltage is out of range. When TS pin is not used, connect a $10\text{-k}\Omega$ resistor from REGN to TS and a $10\text{-k}\Omega$ resistor from TS to GND. It is recommended to use a $103\text{AT-}2$ thermistor. BQ25616 supports hot/cold profile and BQ25616J supports JEITA profile. |  |  |  |

| VAC                                                                              | VAC 1 P VB                                                                                                                                                                                                                                                                                                                                  |                                                                                                       | Charger input voltage sensing. Optional external n-channel ACFET is placed between VAC and VBUS. When VAC voltage is below ACOV threshold (14.2-V) and above UVLO, ACFET turns on to connect VAC to VBUS, and power up the charger IC. Connect VAC and VBUS if ACFET is not to be used.                                                                                                                                                                                                                                       |  |  |  |

| VBUS                                                                             | 24                                                                                                                                                                                                                                                                                                                                          | Р                                                                                                     | Charger input voltage. The internal n-channel reverse block MOSFET (RBFET) is connected between VBUS and PMID with VBUS on source. Place a 1-uF ceramic capacitor <sup>(2)</sup> from VBUS to GND and place it as close as possible to the device.                                                                                                                                                                                                                                                                            |  |  |  |

| $ \begin{tabular}{lllllllllllllllllllllllllllllllllll$                           |                                                                                                                                                                                                                                                                                                                                             | $R_{VSET}$ > 50k $\Omega$ (float pin) = 4.208 V<br>$R_{VSET}$ < 500 $\Omega$ (short to GND) = 4.352 V |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| Thermal<br>Pad                                                                   | _                                                                                                                                                                                                                                                                                                                                           | Р                                                                                                     | Ground reference for the device that is also the thermal pad used to conduct heat from the device. This connection serves two purposes. The first purpose is to provide an electrical ground connection for the device. The second purpose is to provide a low thermal-impedance path from the device die to the PCB. This pad should be tied externally to a ground plane.                                                                                                                                                   |  |  |  |

<sup>(1)</sup> Al = Analog input, AO = Analog Output, AIO = Analog input Output, DI = Digital input, DO = Digital Output, DIO = Digital input Output, P = Power

<sup>(2)</sup> All capacitors are ceramic unless otherwise specified

### 8 Specifications

### 8.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                     |                                                                             | MIN   | MAX | UNIT |

|---------------------|-----------------------------------------------------------------------------|-------|-----|------|

| Voltage             | VAC (converter not switching)                                               | - 2   | 30  | V    |

| Voltage             | VBUS (converter not switching)                                              | -2    | 22  | V    |

| Voltage             | PMID (converter not switching)                                              | - 0.3 | 22  | V    |

| Voltage             | sw                                                                          | - 0.3 | 16  | V    |

| Voltage             | BAT, SYS (converter not switching)                                          | - 0.3 | 7   | V    |

| Voltage             | BTST                                                                        | - 0.3 | 22  | V    |

| Voltage             | ACDRV                                                                       | - 0.3 | 40  | V    |

| Voltage             | D+. D-, STAT, OTG, $\overline{PG}$ , ILIM, $\overline{CE}$ , ICHG, TS, VSET | - 0.3 | 7   | V    |

| Output Sink Current | STAT, PG                                                                    |       | 6   | mA   |

| T <sub>J</sub>      | Junction temperature                                                        | - 40  | 150 | °C   |

| T <sub>stg</sub>    | Storage temperature                                                         | - 55  | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Rating may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Condition. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 8.2 ESD Ratings

|                    |                          |                                                                                          | VALUE | UNIT |

|--------------------|--------------------------|------------------------------------------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> | Electrostatic discharge  | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>              | ±2000 | V    |

| V(ESD)             | Liectrostatic discriarge | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> | ±250  | v    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

### 8.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                   |                       | MIN  | NOM MAX | UNIT |

|-------------------|-----------------------|------|---------|------|

| V <sub>VBUS</sub> | Input voltage         | 4    | 13.5    | V    |

| V <sub>BAT</sub>  | Battery voltage       |      | 4.35    | V    |

| I <sub>VBUS</sub> | Input current         |      | 3.2     | Α    |

| I <sub>SW</sub>   | Output current (SW)   |      | 3.2     | Α    |

|                   | Fast charging current |      | 3       | Α    |

| I <sub>BAT</sub>  | RMS discharge current |      | 6       | Α    |

| T <sub>A</sub>    | Ambient temperature   | - 40 | 85      | °C   |

#### 8.4 Thermal Information

| THERMAL METRIC <sup>(1)</sup> |                                                                | BQ25616/BQ25616J |      |

|-------------------------------|----------------------------------------------------------------|------------------|------|

|                               |                                                                | RTW (WQFN)       | UNIT |

|                               |                                                                | 24 Pins          |      |

| R <sub>0</sub> JA             | Junction-to-ambient thermal resistance (JEDEC <sup>(1)</sup> ) | 31.9             | °C/W |

| R <sub>θ JC(top)</sub>        | Junction-to-case (top) thermal resistance                      | 27               | °C/W |

| R <sub>0</sub> JB             | Junction-to-board thermal resistance                           | 9.2              | °C/W |

| $\Psi_{JT}$                   | Junction-to-top characterization parameter                     | 0.4              | °C/W |

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 8.4 Thermal Information (continued)

|                               |                                              | BQ25616/BQ25616J |      |  |

|-------------------------------|----------------------------------------------|------------------|------|--|

| THERMAL METRIC <sup>(1)</sup> |                                              | RTW (WQFN)       | UNIT |  |

|                               |                                              | 24 Pins          |      |  |

| $\Psi_{JB}$                   | Junction-to-board characterization parameter | 9.2              | °C/W |  |

| R <sub>θ JC(bot)</sub>        | Junction-to-case (bottom) thermal resistance | 2.8              | °C/W |  |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

### 8.5 Electrical Characteristics

$V_{VBUS\_UVLOZ} < V_{VBUS\_OV}$  and  $V_{VBUS} > V_{BAT} + V_{SLEEP}$ ,  $T_J = -40^{\circ}C$  to +125°C, and  $T_J = 25^{\circ}C$  for typical values (unless otherwise noted)

|                            | PARAMETER                                                                          | TEST CONDITIONS                                                                                               | MIN  | TYP  | MAX   | UNIT |

|----------------------------|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|------|------|-------|------|

| QUIESCENT CU               | RRENTS                                                                             |                                                                                                               |      |      |       |      |

| I <sub>Q_BAT</sub>         | Quiescent battery current (BAT, SYS, SW)                                           | VBAT = 4.5V, VBUS floating or VBUS<br>= 0V - 5V, SCL, SDA = 0V or 1.8V, T <sub>J</sub><br>< 85 °C, BATFET on. |      | 9.5  | 15    | μА   |

| I <sub>VBUS</sub>          | Input current (VBUS) in buck mode when converter is switching                      | VBUS=5V, charge disabled, converter switching, ISYS = 0A                                                      |      | 2.3  |       | mA   |

| I <sub>BST</sub>           | Quiescent battery current (BAT, SYS, SW) in boost mode when converter is switching | VBAT = 4.5V, VBUS = 4.9V, boost mode enabled, converter switching, $I_{VBUS} = 0A$                            |      | 2.4  |       | mA   |

| VBUS / VBAT SU             | JPPLY                                                                              |                                                                                                               |      |      |       |      |

| V <sub>VBUS_OP</sub>       | VBUS operating range                                                               |                                                                                                               | 4    |      | 13.5  | V    |

| V <sub>VAC_UVLOZ</sub>     | VAC rising for ACFET turnon, no battery                                            | VAC rising                                                                                                    |      | 3.55 | 3.85  | V    |

| V <sub>VAC_UVLO</sub>      | VAC falling for ACFET turnoff, no battery                                          | VAC falling                                                                                                   |      | 3.25 | 3.55  | V    |

| V <sub>ACDRV</sub>         | External ACFET gate drive voltage with minimum 8nF CGS                             |                                                                                                               |      | 10   |       | V    |

| V <sub>VBUS_UVLOZ</sub>    | VBUS rising for active bias, no battery                                            | VBUS rising                                                                                                   |      | 3.3  | 3.7   | V    |

| V <sub>VBUS_UVLO</sub>     | VBUS falling to turnoff bias, no battery                                           | VBUS falling                                                                                                  |      | 3    | 3.3   | V    |

| V <sub>VBUS_PRESENT</sub>  | VBUS to enable REGN                                                                | VBUS rising                                                                                                   |      | 3.65 | 3.9   | V    |

| V <sub>VBUS_PRESENTZ</sub> | VBUS to disable REGN                                                               | VBUS falling                                                                                                  |      | 3.15 | 3.4   | V    |

| V <sub>SLEEP</sub>         | Enter Sleep mode threshold                                                         | VBUS falling, VBUS - VBAT, VBAT = 4V                                                                          | 15   | 60   | 110   | mV   |

| V <sub>SLEEPZ</sub>        | Exit Sleep mode threshold                                                          | VBUS rising, VBUS - VBAT, VBAT = 4V                                                                           | 115  | 220  | 340   | mV   |

| V                          | VAC overvoltage rising threshold to turnoff ACFET and switching                    | VAC rising                                                                                                    | 13.5 | 14.2 | 14.85 | V    |

| V <sub>ACOV</sub>          | VAC overvoltage falling threshold to turnon ACFET and switching                    | VAC falling,                                                                                                  | 13   | 13.9 | 14.5  | V    |

| V <sub>BAT_UVLOZ</sub>     | BAT voltage for active bias, no VBUS                                               | VBAT rising                                                                                                   | 2.5  |      |       | V    |

| V <sub>BAT_DPLZ</sub>      | BAT depletion rising threshold to turn on BATFET                                   | VBAT rising                                                                                                   | 2.35 |      | 2.8   | V    |

| V <sub>BAT_DPL</sub>       | BAT depletion falling threshold to turn off BATFET                                 | VBAT falling                                                                                                  | 2.18 |      | 2.62  | V    |

| V <sub>POORSRC</sub>       | Bad adapter detection threshold                                                    | VBUS falling                                                                                                  | 3.75 | 3.9  | 4.0   | V    |

| POWER PATH M               | ANAGEMENT                                                                          |                                                                                                               |      |      | l     |      |

| V <sub>SYS_MIN</sub>       | Typical minimum system regulation voltage                                          | VBAT=3.2V < SYS_MIN = 3.5V, ISYS = 0A                                                                         | 3.5  | 3.65 |       | V    |

| V <sub>SYS_OVP</sub>       | System overvoltage threshold                                                       | VREG = 4.35V, Charge disabled, ISYS = 0A                                                                      |      | 4.7  |       | V    |

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

$V_{VBUS\_UVLOZ} < V_{VBUS\_OV}$  and  $V_{VBUS} > V_{BAT} + V_{SLEEP}$ ,  $T_J = -40^{\circ}C$  to +125°C, and  $T_J = 25^{\circ}C$  for typical values (unless otherwise noted)

|                           | PARAMETER                                                  | TEST CONDITIONS                                                                        | MIN    | TYP   | MAX    | UNIT                         |

|---------------------------|------------------------------------------------------------|----------------------------------------------------------------------------------------|--------|-------|--------|------------------------------|

| R <sub>ON_RBFET</sub>     | Blocking FET on-resistance                                 |                                                                                        |        | 45    |        | mΩ                           |

| R <sub>ON_HSFET</sub>     | High-side switching FET on-resistance                      |                                                                                        |        | 62    |        | $\mathbf{m}\Omega$           |

| R <sub>ON_LSFET</sub>     | Low-side switching FET on-resistance                       |                                                                                        |        | 71    |        | $\mathbf{m}\Omega$           |

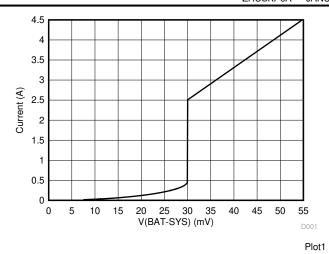

| V <sub>BATFET_FWD</sub>   | BATFET forward voltage in supplement mode                  | BAT discharge current 10mA, converter running                                          |        | 30    |        | mV                           |

| BATTERY CHAP              | RGER                                                       |                                                                                        |        |       |        |                              |

|                           |                                                            | VREG = 4.1V, $R_{VSET}$ =10k $\Omega$ , $T_{J}$ = 0°C - 85°C                           | 4.0836 | 4.1   | 4.1164 | V                            |

| V <sub>REG_ACC</sub>      | Charge voltage accuracy                                    | VREG = 4.2V, R <sub>VSET</sub> >50k Ω , T <sub>J</sub> = 0°C - 85°C                    | 4.1832 | 4.2   | 4.2168 | V                            |

|                           |                                                            | VREG = 4.35V, $R_{VSET}$ <500 $\Omega$ , $T_{J}$ = 0°C - 85°C                          | 4.3326 | 4.35  | 4.3674 | V                            |

| I <sub>CHG_RANGE</sub>    | Typical charge current regulation range                    |                                                                                        | 0      |       | 3      | Α                            |

| K <sub>ICHG</sub>         | ICHG pin setting ratio                                     | ICHG=K <sub>ICHG</sub> /R <sub>ICHG</sub> , VBAT = 3.1V, T <sub>J</sub> = -40°C - 85°C | 639    | 677   | 715    | $\mathbf{A}\mathbf{x}\Omega$ |

| NCHG                      | To the pin setting faile                                   | $ CHG=K_{ICHG}/R_{ICHG}, VBAT = 3.8V, T_J = -40$ °C - 85°C                             | 639    | 677   | 715    | $\mathbf{A}\mathbf{x}\Omega$ |

|                           |                                                            | $R_{ICHG}$ = 1100 $\Omega$ , VBAT = 3.1V or 3.8V, $T_{J}$ = -40°C - 85°C               | 0.516  | 0.615 | 0.715  | Α                            |

| I <sub>CHG_ACC</sub>      | Fast charge current regulation accuracy                    | $R_{ICHG}$ = 562 $\Omega$ , VBAT = 3.1V or 3.8V, $T_{J}$ = -40°C - 85°C                | 1.14   | 1.205 | 1.28   | Α                            |

|                           |                                                            | $R_{ICHG}$ = 372 $\Omega$ , VBAT = 3.1V or 3.8V, $T_{J}$ = -40°C - 85°C                | 1.715  | 1.82  | 1.89   | Α                            |

| I <sub>PRECHG_RATIO</sub> | Precharge current accuracy                                 | As percentage of ICHG, VBAT = 2.6V                                                     |        | 5     |        | %                            |

|                           | Precharge current accuracy                                 | $R_{ICHG}$ = 1100 $\Omega$ , VBAT = 2.6V, $T_J$ = -40°C - 85°C                         | 21     | 30    | 38     | mA                           |

| I <sub>PRECHG_ACC</sub>   |                                                            | $R_{ICHG}$ = 562 $\Omega$ , VBAT = 2.6V, $T_J$ = $-40^{\circ}$ C - 85 $^{\circ}$ C     | 48     | 60    | 67     | mA                           |

|                           |                                                            | $R_{ICHG}$ = 372 $\Omega$ , VBAT = 2.6V, $T_{J}$ = $-40^{\circ}$ C - 85°C              | 76     | 90    | 97     | mA                           |

| I <sub>TERM_RATIO</sub>   | Termination current accuracy                               | As percentage of ICHG, VBAT = 4.35V, (char, all codes)                                 |        | 5     |        | %                            |

|                           |                                                            | $R_{ICHG}$ = 1100 $\Omega$ , VBAT = 4.35V, $T_J$ = 0°C - 85°C                          | 9      | 31    | 57     | mA                           |

| I <sub>TERM_ACC</sub>     | Termination current accuracy                               | $R_{ICHG}$ = 562 $\Omega$ , VBAT = 4.35V, $T_J$ = $0^{\circ}$ C - 85 $^{\circ}$ C      | 36     | 60    | 85     | mA                           |

|                           |                                                            | $R_{ICHG}$ = 372 $\Omega$ , VBAT = 4.35V, $T_J$ = $0^{\circ}$ C - 85 $^{\circ}$ C      | 56     | 91    | 126    | mA                           |

| V <sub>BAT_SHORTZ</sub>   | Battery short voltage rising threshold to start pre-charge | VBAT rising                                                                            | 2.13   | 2.25  | 2.35   | V                            |

| V <sub>BAT_SHORT</sub>    | Battery short voltage falling threshold to stop pre-charge | VBAT falling                                                                           | 1.85   | 2     | 2.15   | V                            |

| I <sub>BAT_SHORT</sub>    | Battery short trickle charging current                     | VBAT < V <sub>BAT_SHORTZ</sub>                                                         | 70     | 90    | 110    | mA                           |

| $V_{BATLOWV}$             | Battery LOWV rising threshold to start fast-charge         | VBAT rising                                                                            | 3      | 3.12  | 3.24   | V                            |

| * BAILOWV                 | Battery LOWV falling threshold to stop fast-charge         | VBAT falling                                                                           | 2.7    | 2.8   | 2.9    | V                            |

| V <sub>RECHG</sub>        | Battery recharge threshold                                 | VBAT falling                                                                           | 90     | 100   | 150    | mV                           |

$V_{VBUS\_UVLOZ} < V_{VBUS\_OV}$  and  $V_{VBUS} > V_{BAT} + V_{SLEEP}$ ,  $T_J = -40^{\circ}\text{C}$  to +125°C, and  $T_J = 25^{\circ}\text{C}$  for typical values (unless otherwise noted)

|                          | PARAMETER                                            | TEST CONDITIONS                               | MIN   | TYP  | MAX   | UNIT |

|--------------------------|------------------------------------------------------|-----------------------------------------------|-------|------|-------|------|

| I <sub>SYS_LOAD</sub>    | System discharge load current during SYSOVP          |                                               |       | 30   |       | mA   |

| D                        | Dettem FFT on mariatana                              | T <sub>J</sub> = -40°C - 85°C                 |       | 19.5 | 26    | mΩ   |

| R <sub>ON_BATFET</sub>   | Battery FET on-resistance                            | T <sub>J</sub> = -40°C - 125°C                |       | 19.5 | 30    | mΩ   |

| BATTERY OVER             | VOLTAGE PROTECTION                                   |                                               |       |      |       |      |

| .,                       | Battery overvoltage rising threshold                 | VBAT rising, as percentage of VREG            | 103   | 104  | 105   | %    |

| $V_{BAT\_OVP}$           | Battery overvoltage falling threshold                | VBAT falling, as percentage of VREG           | 101   | 102  | 103   | %    |

| INPUT VOLTAGE            | / CURRENT REGULATION                                 |                                               |       |      |       |      |

| V <sub>INDPM_ACC</sub>   | Typical input voltage regulation accuracy            |                                               | 4.171 | 4.3  | 4.429 | V    |

| V <sub>INDPM_TRACK</sub> | VINDPM threshold to track battery voltage            | VBAT = 4.35V                                  | 4.45  | 4.55 | 4.74  | V    |

| I <sub>INDPM_ACC</sub>   | Input current regulation accuracy                    | IINDPM = 500mA (T <sub>J</sub> =-40°C - 85°C) | 450   | 465  | 500   | mA   |

| I <sub>INDPM_ACC</sub>   | Input current regulation accuracy                    | IINDPM = 900mA (T <sub>J</sub> =-40°C-85°C)   | 750   | 835  | 900   | mA   |

| I <sub>INDPM_ACC</sub>   | Input current regulation accuracy                    | IINDPM = 1500mA (T <sub>J</sub> =-40°C-85°C)  | 1300  | 1390 | 1500  | mA   |

| K <sub>ILIM</sub>        | ILIM pin setting ratio                               |                                               | 459   | 478  | 500   | ΑχΩ  |

| D+ / D- DETECTI          | ON                                                   |                                               |       |      |       |      |

| V <sub>DP_SRC</sub>      | D+ line source voltage                               |                                               | 500   | 600  | 700   | mV   |

| I <sub>DP_SRC</sub>      | D+ line data contact detect current source           | VD+ = 200 mV                                  | 7     | 10   | 14    | μΑ   |

| I <sub>DP_SINK</sub>     | D+ line sink current                                 | VD+ = 500 mV                                  | 50    | 100  | 150   | μA   |

| V <sub>DP_DAT_REF</sub>  | D+ line data detect voltage                          | D+ pin Rising                                 | 250   |      | 400   | mV   |

| V <sub>DP_LGC_LOW</sub>  | D+ line logic low.                                   | D+ pin Rising                                 |       |      | 800   | mV   |

| R <sub>DP_DWN</sub>      | D+ line pull-down resistance                         | VD+ = 500 mV                                  | 14.25 |      | 24.8  | kΩ   |

| I <sub>D+_LKG</sub>      | Leakage current into D+ line                         | Pull up to 1.8 V                              | - 1   |      | 1     | μA   |

| V <sub>DM_SRC</sub>      | D- line source voltage                               |                                               | 500   | 600  | 700   | mV   |

| I <sub>DM_SINK</sub>     | D- line sink current                                 | VD- = 500 mV                                  | 50    | 100  | 150   | μA   |

| V <sub>DM_DAT_REF</sub>  | D- line data detect voltage                          | D- pin Rising                                 | 250   |      | 400   | mV   |

| R <sub>DM_DWN</sub>      | D- line pull-down resistance                         | VD- = 500 mV                                  | 14.25 |      | 24.8  | kΩ   |

| I <sub>DLKG</sub>        | Leakage current into D- line                         | Pull up to 1.8 V                              | - 1   |      | 1     | μA   |

| V <sub>D+ _2p8_hi</sub>  | D+ High comparator threshold for 2.8V detection      | D+ pin rising                                 | 2.85  | 3    | 3.1   | V    |

| V <sub>D+ _2p8_lo</sub>  | D+ Low comparator threshold for 2.8V detection       | D+ pin rising                                 | 2.35  | 2.45 | 2.55  | V    |

| V <sub>D+ _2p8</sub>     | D+ comparator threshold for non-<br>standard adapter |                                               | 2.55  |      | 2.85  | V    |

| V <sub>D2p8_hi</sub>     | D- High comparator threshold for 2.8V detection      | D- pin rising                                 | 2.85  | 3    | 3.1   | V    |

| V <sub>D2p8_lo</sub>     | D- Low comparator threshold for 2.8V detection       | D- pin rising                                 | 2.35  | 2.45 | 2.55  | V    |

| V <sub>D2p8</sub>        | D- comparator threshold for non-<br>standard adapter |                                               | 2.55  |      | 2.85  | ٧    |

| V <sub>D+ _2p0_hi</sub>  | D+ High comparator threshold for 2.0V detection      | D+ pin rising                                 | 2.15  | 2.25 | 2.35  | ٧    |

| V <sub>D+ _2p0_lo</sub>  | D+ Low comparator threshold for 2.0V detection       | D+ pin rising                                 | 1.6   | 1.7  | 1.85  | V    |

$V_{VBUS\_UVLOZ} < V_{VBUS\_OV}$  and  $V_{VBUS} > V_{BAT} + V_{SLEEP}$ ,  $T_J = -40^{\circ}C$  to +125°C, and  $T_J = 25^{\circ}C$  for typical values (unless otherwise noted)

|                          | PARAMETER                                                                                             | TEST CONDITIONS                          | MIN   | TYP   | MAX   | UNIT |

|--------------------------|-------------------------------------------------------------------------------------------------------|------------------------------------------|-------|-------|-------|------|

| V <sub>D+_2p0</sub>      | D+ comparator threshold for non-<br>standard adapter                                                  |                                          | 1.85  |       | 2.15  | V    |

| V <sub>D2p0_hi</sub>     | D- High comparator threshold for 2.0V detection                                                       | D- pin rising                            | 2.15  | 2.25  | 2.35  | V    |

| V <sub>D2p0_lo</sub>     | D- Low comparator threshold for 2.0V detection                                                        | D- pin rising                            | 1.6   | 1.7   | 1.85  | V    |

| V <sub>D2p0</sub>        | D- comparator threshold for non-<br>standard adapter                                                  |                                          | 1.85  |       | 2.15  | V    |

| V <sub>D+ _1p2_hi</sub>  | D+ High comparator threshold for 1.2V detection                                                       | D+ pin rising                            | 1.35  | 1.5   | 1.6   | V    |

| V <sub>D+ _1p2_lo</sub>  | D+ Low comparator threshold for 1.2V detection                                                        | D+ pin rising                            | 0.85  | 0.95  | 1.05  | V    |

| V <sub>D+_1p2</sub>      | D+ comparator threshold for non-<br>standard adapter                                                  |                                          | 1.05  |       | 1.35  | V    |

| V <sub>D1p2_hi</sub>     | D- High comparator threshold for 1.2V detection                                                       | D- pin rising                            | 1.35  | 1.5   | 1.6   | V    |

| V <sub>D1p2_lo</sub>     | D- Low comparator threshold for 1.2V detection                                                        | D- pin rising                            | 0.85  | 0.95  | 1.05  | V    |

| V <sub>D1p2</sub>        | D- comparator threshold for non-<br>standard adapter                                                  |                                          | 1.05  |       | 1.35  | V    |

| THERMAL REG              | GULATION AND THERMAL SHUTDOWN                                                                         |                                          |       |       |       |      |

| T <sub>REG</sub>         | Junction temperature regulation accuracy                                                              |                                          |       | 110   |       | °C   |

| T <sub>SHUT</sub>        | Thermal Shutdown Rising threshold                                                                     | Temperature Increasing                   |       | 150   |       | °C   |

|                          | Thermal Shutdown Falling threshold                                                                    | Temperature Decreasing                   |       | 130   |       | °C   |

| CHARGE MOD               | E THERMISTOR COMPARATOR (JEITA 6                                                                      | 16J or HOT/COLD 616)                     |       |       | 1     |      |

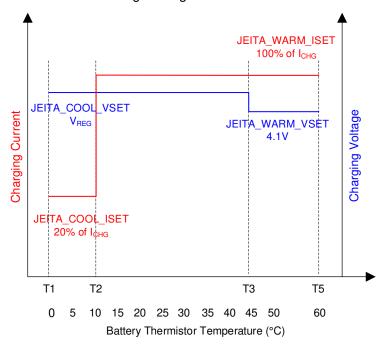

| V <sub>T1_RISE%</sub>    | TS pin voltage rising threshold,<br>Charge suspended above this voltage.                              | As Percentage to REGN (0°C w/ 103AT)     | 72.4  | 73.3  | 74.2  | %    |

| V <sub>T1_FALL</sub> %   | TS pin voltage falling threshold. Charge re-enabled to 20% of ICHG and VREG below this voltage.       | As Percentage to REGN                    | 71.5  | 72    | 72.5  | %    |

| V <sub>T2_RISE</sub> %   | TS pin voltage rising threshold,<br>Charge back to 20% of ICHG and<br>VREG above this voltage (616J). | As Percentage to REGN (10°C w/<br>103AT) | 67.75 | 68.25 | 68.75 | %    |

| V <sub>T2_FALL</sub> %   | TS pin voltage falling threshold.<br>Charge back to ICHG and VREG<br>below this voltage (616J)        | As Percentage to REGN                    | 66.45 | 66.95 | 67.45 | %    |

| V <sub>T3_FALL</sub> %   | TS pin voltage falling threshold.<br>Charge back to ICHG and VREG<br>below this voltage (616J)        | As Percentage to REGN (45°C w/ 103AT)    | 44.25 | 44.75 | 45.25 | %    |

| V <sub>T3_RISE</sub> %   | TS pin voltage rising threshold. Charge back to ICHG and VREG above this voltage. (616J)              | As Percentage to REGN                    | 45.55 | 46.05 | 46.55 | %    |

| V <sub>T5_FALL</sub> %   | TS pin voltage falling threshold, charge suspended below this voltage.                                | As Percentage to REGN (60°C w/ 103AT)    | 33.7  | 34.2  | 35.1  | %    |

| V <sub>T5_RISE</sub> %   | TS pin voltage rising threshold. Charge back to ICHG and 4.1V above this voltage.                     | As Percentage to REGN                    | 35    | 35.5  | 36    | %    |

| V <sub>T1_RISE_HC%</sub> | TS pin voltage rising threshold.<br>Charge suspended above this voltage.<br>(616)                     | As Percentage to REGN (0°C w/ 103AT)     | 72.4  | 73.3  | 74.2  | %    |

$V_{VBUS\_UVLOZ} < V_{VBUS\_OV}$  and  $V_{VBUS} > V_{BAT} + V_{SLEEP}$ ,  $T_J = -40^{\circ}\text{C}$  to +125°C, and  $T_J = 25^{\circ}\text{C}$  for typical values (unless otherwise noted)

|                           | PARAMETER                                                                               | TEST CONDITIONS                                  | MIN   | TYP     | MAX   | UNIT  |

|---------------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------|-------|---------|-------|-------|

|                           | TS pin voltage falling threshold.                                                       | 1201 CONDITIONS                                  |       | • • • • | Wirth | Oitii |

| V <sub>T1_FALL_HC%</sub>  | Charge back to ICHG and VREG below this voltage. (616)                                  | As Percentage to REGN                            | 71    | 72      | 73    | %     |

| V <sub>T3_FALL_HC</sub> % | TS pin voltage falling threshold.<br>Charge suspended below this voltage.<br>(616)      | As Percentage to REGN (45°C w/ 103AT)            | 44.25 | 44.75   | 45.25 | %     |

| V <sub>T3_RISE_HC%</sub>  | TS pin voltage rising threshold. Charge back to ICHG and VREG above this voltage. (616) | As Percentage to REGN                            | 45.55 | 46.05   | 46.55 | %     |

| BOOST MODE 1              | THERMISTOR COMPARATOR (HOT/COL                                                          | D)                                               |       |         | '     |       |

| V <sub>BCOLD_RISE</sub> % | TS pin voltage rising threshold, boost mode is suspended above this voltage.            | As Percentage to REGN ( - 19.5°C w/ 103AT)       | 79.5  | 80      | 80.5  | %     |

| V <sub>BCOLD_FALL</sub> % | TS pin voltage falling threshold                                                        | As Percentage to REGN (0°C w/ 103AT)             |       | 72      |       | %     |

| V <sub>BHOT_FALL</sub> %  | TS pin voltage threshold. boost mode is suspended below this voltage.                   | As Percentage to REGN, (64°C w/ 103AT)           | 30.2  | 31.2    | 32.2  | %     |

| V <sub>BHOT_RISE</sub> %  | TS pin voltage rising threshold                                                         | As Percentage to REGN, (45°C w/ 103AT)           |       | 44      |       | %     |

| CHARGE OVER               | CURRENT COMPARATOR (CYCLE-BY-C                                                          | CYCLE)                                           |       |         | '     |       |

| I <sub>HSFET_OCP</sub>    | HSFET cycle-by-cycle overcurrent threshold                                              |                                                  | 5.2   |         | 8.0   | Α     |

| SWITCHING CO              | NVERTER                                                                                 |                                                  |       |         | 1     |       |

| F <sub>SW</sub>           | PWM switching frequency                                                                 | Oscillator frequency                             | 1.32  | 1.5     | 1.68  | MHz   |

| D <sub>MAX</sub>          | Maximum PWM Duty Cycle                                                                  |                                                  |       | 97      |       | %     |

| BOOST MODE O              | CONVERTER                                                                               |                                                  |       |         | I     |       |

|                           | Battery voltage exiting boost mode                                                      | V <sub>VBAT</sub> falling                        | 2.6   | 2.8     | 2.9   | V     |

| $V_{BATLOWV\_OTG}$        | Battery voltage entering boost mode                                                     | V <sub>VBAT</sub> rising                         | 2.9   | 3.0     | 3.15  | V     |

| V <sub>BST_ACC</sub>      | Boost mode voltage regulation accuracy                                                  | IVBUS = 0A, BOOST_V = 5V                         | 4.85  | 5       | 5.15  | V     |

| I <sub>BST_ACC</sub>      | Boost mode current regulation accuracy                                                  |                                                  | 1.2   | 1.4     | 1.6   | Α     |

| I <sub>SYS_OCP_Q4</sub>   | Boost mode battery discharge current clamp on BATFET Q4                                 |                                                  | 9     | 10      |       | Α     |

| REGN LDO                  |                                                                                         |                                                  |       |         |       |       |

| \/                        | DECNI DO cuitout valta a                                                                | V <sub>VBUS</sub> = 5V, I <sub>REGN</sub> = 20mA | 4.58  | 4.7     | 4.8   | V     |

| $V_{REGN}$                | REGN LDO output voltage                                                                 | V <sub>VBUS</sub> = 9V, I <sub>REGN</sub> = 20mA | 5.6   | 6       | 6.5   | V     |

| I <sub>REGN</sub>         | REGN LDO current limit                                                                  | V <sub>VBUS</sub> = 5V, V <sub>REGN</sub> = 3.8V | 50    |         |       | mA    |

| LOGIC INPUT P             | IN                                                                                      |                                                  |       |         | 1     |       |

| V <sub>IH</sub>           | Input high threshold level (/CE)                                                        |                                                  | 1.3   |         |       | V     |

| V <sub>IL</sub>           | Input low threshold level (/CE)                                                         |                                                  |       |         | 0.4   | V     |

| I <sub>IN_BIAS</sub>      | High-level leakage current (/CE)                                                        | Pull up rail 1.8V                                |       |         | 1     | μA    |

| LOGIC OUTPUT              | PIN                                                                                     |                                                  |       |         |       |       |

| V <sub>OL</sub>           | Output low threshold level (STAT, /PG)                                                  | Sink current = 5mA                               |       |         | 0.4   | V     |

| I <sub>OUT BIAS</sub>     | High-level leakage current (STAT, /PG)                                                  | Pull up rail 1.8V                                |       |         | 1     | μΑ    |

Submit Document Feedback

# 8.6 Timing Requirements

|                            |                                       | MIN | NOM | MAX | UNIT |  |  |  |

|----------------------------|---------------------------------------|-----|-----|-----|------|--|--|--|

| VBUS / VBAT POW            | VBUS / VBAT POWER UP                  |     |     |     |      |  |  |  |

| t <sub>POORSRC</sub>       | Bad adapter detection duration        |     | 30  |     | ms   |  |  |  |

| t <sub>POORSRC_RETRY</sub> | Bad adapter detection retry wait time |     | 2   |     | s    |  |  |  |

| BATTERY CHARGE             | BATTERY CHARGER                       |     |     |     |      |  |  |  |

| t <sub>TERM_DGL</sub>      | Deglitch time for charge termination  |     | 30  |     | ms   |  |  |  |

| t <sub>RECHG_DGL</sub>     | Deglitch time for recharge threshold  |     | 30  |     | ms   |  |  |  |

| t <sub>TOP_OFF</sub>       | Typical top-off timer                 |     | 30  |     | min  |  |  |  |

| t <sub>SAFETY</sub>        | Charge safety timer accuracy          | 8   | 10  | 12  | hr   |  |  |  |

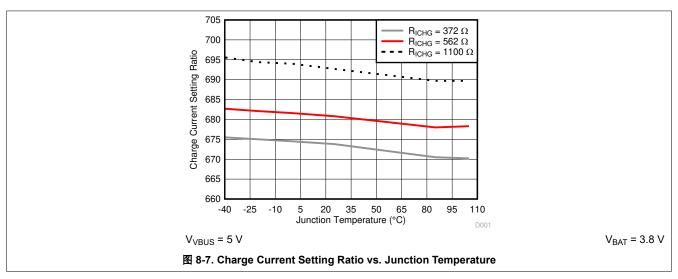

### 8.7 Typical Characteristics

# 8.7 Typical Characteristics (continued)

### 9 Detailed Description

### 9.1 Overview

The BQ25616/616J device is a highly integrated 3.0-A switch-mode battery charger for single cell Li-ion and Lipolymer battery. It includes an input reverse-blocking FET (RBFET, Q1), high-side switching FET (HSFET, Q2), low-side switching FET (LSFET, Q3), and battery FET (BATFET, Q4), and bootstrap diode for the high-side gate drive.

### 9.2 Functional Block Diagram

#### 9.3 Feature Description

#### 9.3.1 Power-On-Reset (POR)

The device powers internal bias circuits from the higher voltage of VBUS and BAT. When  $V_{VBUS}$  rises above  $V_{VBUS\_UVLOZ}$  or  $V_{BAT}$  rises above  $V_{BAT\_UVLOZ}$ , the sleep comparator, battery depletion comparator, and BATFET driver are active.

#### 9.3.2 Device Power Up From Battery Without Input Source

If only the battery is present and the voltage is above depletion threshold (V<sub>BAT\_DPLZ</sub>), the BATFET turns on and connects the battery to the system. The REGN stays off to minimize the quiescent current. The low R<sub>DSON</sub> of BATFET and the low quiescent current on BAT minimize the conduction loss and maximize the battery run time.

The device always monitors the discharge current through the BATFET. When the system is overloaded or shorted ( $I_{BAT} > I_{SYS OCP Q4}$ ), the device turns off BATFET immediately until the input source plugs in again.

### 9.3.3 Power Up From Input Source

When an input source is plugged in, the device checks the input source voltage to turn on the REGN LDO and all the bias circuits. It detects and sets the input current limit before the buck converter is started. The power-up sequence from input source is as listed:

- 1. Power Up ACFET, see 节 9.3.3.1 (optional)

- 2. Power Up REGN LDO, see 节 9.3.3.2

- 3. Poor Source Qualification, see # 9.3.3.3

- 4. Input Source Type Detection is based on D+/D to set default input current limit (IINDPM threshold), see 节 9.3.3.4

- 5. Input Voltage Limit Threshold Setting (VINDPM threshold), see 节 9.3.3.5

- 6. Power Up Converter, see 节 9.3.3.6

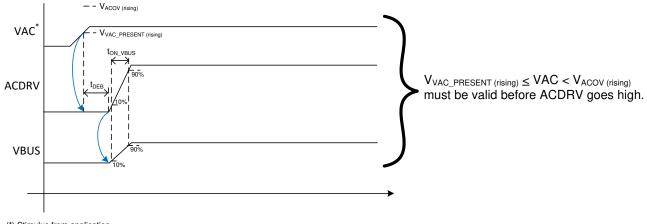

#### 9.3.3.1 Power Up ACFET

The external ACFET provides an additional layer of voltage protection for the device. During input surge up to 30 V, the charger turns off ACFET and converter with 130-ns response time to disconnect VBUS from VAC. If users don't need ACFET, they shall connect VAC to VBUS and keep ACDRV pin floating. The ACFET is enabled when all the below conditions are valid.

The ACFET is enabled when all the below conditions are valid.

- V<sub>VAC PRESENT</sub> < V<sub>VAC</sub> < V<sub>ACOV</sub>.

- After t<sub>DEB</sub> (15 ms typ) delay is completed

If one of the above conditions is not valid, ACFET keeps off. The battery powers the system If it is present.

(\*) Stimulus from application

Note: beginning of blue lines indicate the trigger, and the arrow end of the blue line indicates the action

图 9-1. ACFET Startup Control

### 9.3.3.2 Power Up REGN LDO

The REGN LDO supplies internal bias circuits as well as the HSFET and LSFET gate drive. It also provides the bias rail to TS external resistors. The pull-up rail of STAT can be connected to REGN as well. The REGN LDO is enabled when all the below conditions are valid:

- V<sub>VBUS</sub> > V<sub>VBUS</sub> UVLOZ

- In buck mode, ACFET turns on, V<sub>VBUS</sub> > V<sub>BAT</sub> + V<sub>SLEEPZ</sub>

- In boost mode, V<sub>VBUS</sub> < V<sub>BAT</sub> + V<sub>SLEEPZ</sub>

- · After 220-ms delay is completed

During high impedance mode, REGN LDO turns off. The battery powers up the system.

#### 9.3.3.3 Poor Source Qualification

After the REGN LDO powers up, the device starts to check current capability of the input source. The first step is poor source detection.

VBUS voltage above V<sub>POORSRC</sub> when pulling I<sub>BADSRC</sub> (typical 30 mA)

If the device fails the poor source detection, it repeats poor source qualification every 2 seconds.

#### 9.3.3.4 Input Source Type Detection (IINDPM Threshold)

After poor source detection, the device runs input source detection through D+/D - lines . The D+/D - detection follows the USB Battery Charging Specification 1.2 (BC1.2) to detect standard (SDP/CDP/DCP) and non-standard adapters through USB D+/D - lines.

#### 9.3.3.4.1 D+/D - Detection Sets Input Current Limit

The device contains a D+/D - based input source detection to set the input current limit when a 5-V adapter is plugged-in. The D+/D - detection includes standard USB BC1.2 and non-standard adapters. When an input source is plugged in, the device starts standard USB BC1.2 detection. The USB BC1.2 is capable of identifying Standard Downstream Port (SDP), Charging Downstream Port (CDP) and Dedicated Charging Port (DCP). The non-standard detection is used to distinguish vendor specific adapters (Apple and Samsung) based on their unique dividers on the D+/D - pins. If an adapter is detected as DCP, the input current limit is set at 2.4-A. If an adapter is detected as unknown, the input current limit is set by ILIM pin .

The D+/D - automatically runs when adapter plugs in. The D+/D - detection contains three steps, DCD (Data Contact Detection), primary detection, and secondary detection.

Instruments

DCD (Data Contact Detection) uses a current source to detect when the D+/D - pins have made contact during an attach event. The protocol for data contact detect is as follows:

- Detect VBUS present and VBUS\_GD (pass poor source detection)

- Turn on D+ I<sub>DP SRC</sub> and the D pull-down resistor R<sub>DM DWN</sub> for 13 ms

- If the USB connector is properly attached, the D+ line goes from HIGH to LOW, wait up to 0.5 sec. When the DCD timer of 0.5 sec is expired, the non-standard adapter detection is applied to set the input current limit.

- Turn off I<sub>DP SRC</sub> and disconnect R<sub>DM DWN</sub>

The primary detection is used to distinguish between USB host (Standard Down Stream Port, or SDP) and different type of charging ports (Charging Down Stream Port, or CDP, and Dedicated Charging Port, or DCP). The protocol for primary detection is as follows:

- Turn on  $V_{DP}$  SRC on D+ and  $I_{DM}$  Sink on D for 40 ms

- If portable device is attached to a USB host (SDP), the D is below V<sub>REF\_DAT</sub>. Otherwise, it is attached to either CDP or DCP.

- Turn off  $V_{DP}$  SRC and  $I_{DM}$  Sink

The secondary detection is used to distinguish two types of charging ports (CDP and DCP). The protocol for secondary detection is as follows:

- Turn on V<sub>DM SRC</sub> on D- and I<sub>DP Sink</sub> on D+ for 40 ms

- If portable device is attached to a Charging Downstream Port (CDP), the D+ is below V<sub>DAT\_REF</sub>. Otherwise, it is attached to DCP.

- Turn off V<sub>DM SRC</sub> and I<sub>DP Sink</sub>

Most of the time, a CDP requires the portable device (such as smart phone, tablet) to send back an enumeration within 2.5 seconds of CDP plug-in. Otherwise, the port will power cycle back to SDP even the D+/D - detection indicates CDP.

| The state of the s |                                              |                                              |                         |  |  |  |