**TPS51117**

SLVS631C - DECEMBER 2005 - REVISED MAY 2015

# **TPS51117 Single Synchronous Step-Down Controller**

#### **Features**

- High Efficiency, Low Power Consumption, 4.5-µA Typical Shutdown Current

- Fixed Frequency Emulated On-Time Control, Adjustable from 100 kHz to 550 kHz

- D-CAP™ Mode With 100-ns Load Step Response

- < 1% Initial Reference Accuracy

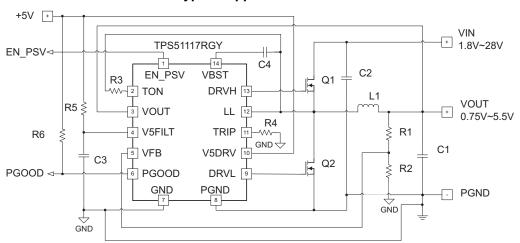

- Output Voltage Range: 0.75 V to 5.5 V

- Wide Input Voltage Range: 1.8 V to 28 V

- Selectable Auto-Skip/PWM-Only Operation

- Temperature Compensated (4500 ppm/°C) Low-Side R<sub>DS(on)</sub> Overcurrent Sensing

- **Negative Overcurrent Limit**

- Integrated Boost Diode

- Integrated OVP/UVP and Thermal Shutdown

- Powergood Signal

- Internal 1.2-ms Voltage Soft-Start

- Integrated Output Discharge (Soft-Stop)

## **Applications**

- **Notebook Computers**

- I/O Supplies

- System Power Supplies

#### 3 **Description**

TPS51117 The device is а cost-effective. synchronous buck controller for POL voltage regulation in notebook PC applications. The controller is dedicated for the operation of the Adaptive On-Time D-CAP mode. This mode provides ease-of-use, low external component count, and fast transient response. Auto-skip mode for high efficiency down to the milliampere load range, or PWM-only mode for low-noise operation is selectable.

The current-sensing scheme for positive overcurrent and negative overcurrent protection is loss-less lowside R<sub>DS(on)</sub> sensing plus temperature compensation. device receives а 5-V (4.5)5.5 V) supply from another regulator such as the TPS51120 or TPS51020. The conversion input can be either VBAT or a 5-V rail, ranging from 1.8 V to 28 V, and the output voltage range is from 0.75 V to 5.5 V.

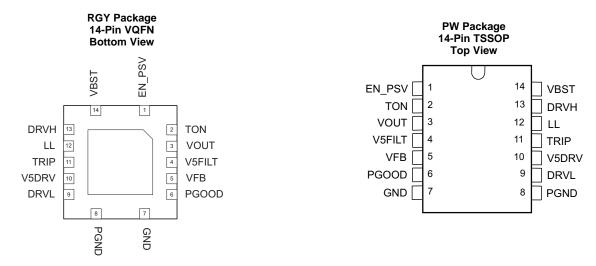

The TPS51117 is available in a 14-pin VQFN or a 14pin TSSOP package and is specified from -40°C to 85°C.

## Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE    | BODY SIZE (NOM)   |  |  |

|-------------|------------|-------------------|--|--|

| TD054447    | TSSOP (14) | 4.40 mm × 5.00 mm |  |  |

| TPS51117    | VQFN (14)  | 3.50 mm × 3.50 mm |  |  |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

#### Typical Application Circuit

## **Table of Contents**

| 1 | Features 1                           |    | 8.1 Application Information                      | 10               |

|---|--------------------------------------|----|--------------------------------------------------|------------------|

| 2 | Applications 1                       |    | 8.2 Typical Application                          | 16               |

| 3 | Description 1                        |    | 8.3 System Examples                              | 20               |

| 4 | Revision History                     | 9  | Power Supply Recommendations                     | 2 <sup>′</sup>   |

| 5 | Pin Configuration and Functions      | 10 | Layout                                           | 2 <sup>′</sup>   |

| 6 | Specifications4                      |    | 10.1 Layout Guidelines                           | 2                |

| • | 6.1 Absolute Maximum Ratings         |    | 10.2 Layout Example                              |                  |

|   | 6.2 Recommended Operating Conditions |    | 10.3 Thermal Considerations                      | 22               |

|   | 6.3 Electrical Characteristics       | 11 | Device and Documentation Support                 | 23               |

|   | 6.4 Typical Characteristics          |    | 11.1 Device Support                              | <mark>2</mark> : |

| 7 | Detailed Description                 |    | 11.2 Community Resources                         | 2                |

| • | 7.1 Overview                         |    | 11.3 Trademarks                                  | 2                |

|   | 7.2 Functional Block Diagram         |    | 11.4 Electrostatic Discharge Caution             | 2                |

|   | 7.3 Feature Description              |    | 11.5 Glossary                                    | <mark>2</mark> : |

|   | 7.4 Device Functional Modes14        | 12 | Mechanical, Packaging, and Orderable Information | 2:               |

| 8 | Application and Implementation 16    |    |                                                  | 2                |

## 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

# Changes from Revision B (September 2009) to Revision C Added Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section. Changes from Revision A (June 2009) to Revision B Page

# 5 Pin Configuration and Functions

## **Pin Functions**

| PIN    |     | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                       |

|--------|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME   | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                       |

| DRVH   | 13  | 0   | High-side NFET gate driver output. Source 5 $\Omega$ , sink 1.5- $\Omega$ LL-node referenced driver. Drive voltage corresponds to VBST to LL voltage.                                                                                                                                                             |

| DRVL   | 9   | 0   | Rectifying (low-side) NFET gate driver output. Source 5 $\Omega$ , sink 1.5- $\Omega$ PGND referenced driver. Drive voltage is V5DRV voltage.                                                                                                                                                                     |

| EN_PSV | 1   | ı   | Enable / power save pin. Connect to ground to disable SMPS. Connect to 3.3 V or 5 V to turn on SMPS and activate skip mode. Float to turn on SMPS but disable skip mode (forced continuous conduction mode).                                                                                                      |

| GND    | 7   | I   | Signal ground pin.                                                                                                                                                                                                                                                                                                |

| LL     | 12  | I/O | High-side NFET gate driver return. Also serves as anode of overcurrent comparator.                                                                                                                                                                                                                                |

| PGND   | 8   | I/O | Ground return for rectifying NFET gate driver. Also cathode of overcurrent protection and source node of the output discharge switch.                                                                                                                                                                             |

| PGOOD  | 6   | 0   | Powergood window comparator, open-drain, output. Pull up to 5-V rail with a pullup resistor. Current capability is 7.5 mA.                                                                                                                                                                                        |

| TON    | 2   | I   | On-time / frequency adjustment pin. Connect to LL with 100-k $\Omega$ to 600-k $\Omega$ resistor.                                                                                                                                                                                                                 |

| TRIP   | 11  | ı   | Overcurrent trip point set input. Connect resistor from this pin to signal ground to set threshold for both overcurrent and negative overcurrent limit.                                                                                                                                                           |

| VBST   | 14  | I   | Supply input for high-side NFET gate driver (boost terminal). Connect capacitor from this pin to LL-node. An internal PN diode is connected between V5DRV to this pin. Designer can add external Schottky diode if forward drop is critical to drive the power NFET.                                              |

| VFB    | 5   | ı   | SMPS voltage feedback input. Connect the resistor divider here for adjustable output.                                                                                                                                                                                                                             |

| VOUT   | 3   | I   | Connect to SMPS output. This terminal serves two functions: output voltage monitor for on-time adjustment, and input for the output discharge switch.                                                                                                                                                             |

| V5DRV  | 10  | I   | 5-V Power supply input for FET gate drivers. Internally connected to VBST by a PN diode. Connect 1 μF or more between this pin and PGND to support instantaneous current for gate drivers.                                                                                                                        |

| V5FILT | 4   | I   | 5-V Power supply input for all the control circuitry except gate drivers. Supply 5-V ramp rate should be 17 mV/ $\mu$ s or less and T $_j$ < 85°C to secure safe start-up of the internal reference circuit. Apply RC filter consists of 300 $\Omega$ + 1 $\mu$ F or 100 $\Omega$ + 4.7 $\mu$ F at the pin input. |

# 6 Specifications

# 6.1 Absolute Maximum Ratings<sup>(1)</sup>

|                    |                                                              |                           | MIN         | MAX | UNIT |

|--------------------|--------------------------------------------------------------|---------------------------|-------------|-----|------|

|                    |                                                              | VBST                      | -0.3        | 36  |      |

|                    |                                                              | VBST (with respect to LL) | -0.3        | 6   |      |

| 1                  | Input voltage EN_PSV, TRIP, V5DRV, V5FILT                    |                           | -0.3        | 6   | V    |

|                    |                                                              | VOUT                      | -0.3        | 6   |      |

|                    |                                                              | TON                       | -0.3        | 6   |      |

|                    |                                                              | DRVH                      | -1          | 36  |      |

|                    |                                                              | DRVH (with respect to LL) | -0.3        | 6   |      |

| (                  | Output voltage                                               | LL                        | -1          | 30  | V    |

|                    |                                                              | PGOOD, DRVL               | -0.3        | 6   |      |

|                    |                                                              | PGND                      | -0.3        | 0.3 |      |

| T <sub>A</sub> (   | Operating free-air te                                        | emperature                | -40         | 85  | °C   |

| T <sub>J</sub>     | Junction temperature                                         |                           | -40         | 125 | °C   |

| L                  | Lead temperature 1.6 mm (1/16 inch) from case for 10 seconds |                           |             | 260 | °C   |

| T <sub>stg</sub> S | Storage temperature                                          | Э                         | <b>-</b> 55 | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                                |                             | MIN  | MAX | UNIT |

|------------------------------------------------|-----------------------------|------|-----|------|

| Supply input voltage                           |                             | 4.5  | 5.5 | V    |

|                                                | VBST                        | 4.5  | 34  |      |

|                                                | VBST (with respect to LL)   | 4.5  | 5.5 |      |

| Input voltage                                  | EN_PSV, TRIP, V5DRV, V5FILT | -0.1 | 5.5 | V    |

|                                                | VOUT                        | -0.1 | 5.5 |      |

|                                                | TON                         | -0.1 | 5.5 |      |

|                                                | DRVH                        | -0.8 | 34  |      |

|                                                | DRVH (with respect to LL)   | -0.1 | 5.5 |      |

| Output voltage                                 | LL                          | -0.8 | 28  | V    |

|                                                | PGOOD, DRVL                 | -0.1 | 5.5 |      |

|                                                | PGND                        | -0.1 | 0.1 |      |

| Operating free-air temperature, T <sub>A</sub> |                             | -40  | 85  | °C   |

#### 6.3 Electrical Characteristics

over operating free-air temperature range (unless otherwise noted)

|                         | ting free-air temperature rang PARAMETER | TEST CONDITIONS                                                                          | MIN     | TYP  | MAX  | UNIT  |

|-------------------------|------------------------------------------|------------------------------------------------------------------------------------------|---------|------|------|-------|

| SUPPLY C                |                                          | . 201 001151110110                                                                       |         |      |      | 31111 |

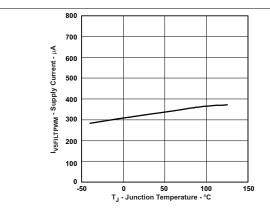

| 30FFLI C                | ORRENI                                   | V5FILT + V5DRV current, PWM, EN_PSV =                                                    |         |      |      |       |

| I <sub>V5FILTPWM</sub>  | float, VFB = 0.77 V, LL = -0.1 V         |                                                                                          |         | 400  | 750  | μA    |

| I <sub>V5FILTSKIP</sub> | Supply current                           | V5FILT + V5DRV current, auto-skip, EN_PSV = 5 V, VFB = 0.77 V, LL = 0.5 V                |         | 250  | 470  | μΑ    |

| I <sub>V5DRVSDN</sub>   | V5DRV shutdown current                   | V5DRV current, EN_PSV = 0 V                                                              |         | 0    | 1    | μΑ    |

| I <sub>V5FILTSDN</sub>  | V5FILT shutdown current                  | V5FILT current, EN_PSV = 0 V                                                             |         | 4.5  | 7.5  | μΑ    |

| VOUT AND                | VFB VOLTAGES                             |                                                                                          |         |      |      |       |

| V <sub>OUT</sub>        | Output voltage                           | Adjustable output range                                                                  | 0.75    |      | 5.5  | V     |

| $V_{VFB}$               | VFB regulation voltage                   |                                                                                          |         | 750  |      | mV    |

|                         |                                          | T <sub>A</sub> = 25°C, bandgap initial accuracy                                          | -0.9%   |      | 0.9% |       |

| $V_{VFB\_TOL}$          | VFB regulation voltage                   | $T_A = 0$ °C to 85°C                                                                     | -1.3%   |      | 1.3% |       |

|                         | tolerance                                | $T_{\Delta} = -40^{\circ}\text{C to } 85^{\circ}\text{C}$                                | -1.6%   |      | 1.6% |       |

| I <sub>VFB</sub>        | VFB input current                        | V <sub>FB</sub> = 0.75 V, absolute value                                                 |         | 0.02 | 0.1  | μA    |

| R <sub>Dischg</sub>     | VOUT discharge resistance                | EN_PSV = 0 V, V <sub>OUT</sub> = 0.5 V                                                   |         | 20   | 32   | Ω     |

|                         | IMER AND INTERNAL SOFT-S                 |                                                                                          |         |      | 02   |       |

| T <sub>ONN</sub>        | Nominal on-time                          | $V_{LL} = 12 \text{ V}, V_{OUT} = 2.5 \text{ V}, R_{TON} = 250 \text{ k}\Omega$          |         | 750  |      | ns    |

| T <sub>ONF</sub>        | Fast on-time                             | $V_{LL} = 12 \text{ V}, V_{OUT} = 2.5 \text{ V}, R_{TON} = 100 \text{ k}\Omega$          | 264     | 330  | 396  | ns    |

| T <sub>ONS</sub>        | Slow on-time                             | $V_{LL} = 12 \text{ V}, V_{OUT} = 2.5 \text{ V}, R_{TON} = 400 \text{ k}\Omega$          | 201     | 1169 | 000  | ns    |

| T <sub>ON(MIN)</sub>    | Minimum on-time                          | $V_{OUT} = 0.75 \text{ V}, R_{TON} = 100 \text{ k}\Omega \text{ to } 28 \text{ V}^{(1)}$ | 80      | 110  | 140  | ns    |

| T <sub>OFF(MIN)</sub>   | Minimum off-time                         | $V_{FB} = 0.7 \text{ V}, LL = -0.1 \text{ V},$                                           |         | 440  | 140  | ns    |

| T <sub>SS</sub>         | Internal soft-start time                 | TRIP = open Time from EN_PSV > 3 V to V <sub>FB</sub> regulation value = 0.735 V         | 0.82    | 1.2  | 1.5  | ms    |

| OUTPUT D                | RIVERS                                   |                                                                                          |         |      |      |       |

|                         |                                          | Source, V <sub>VBST-DRVH</sub> = 0.5 V                                                   |         | 5    | 7    |       |

| $R_{DRVH}$              | DRVH resistance                          | Sink, V <sub>DRVH-LL</sub> = 0.5 V                                                       |         | 1.5  | 2.5  | Ω     |

|                         |                                          | Source, $V_{V5DRV-DRVL} = 0.5 \text{ V}$                                                 |         | 5    | 7    |       |

| $R_{DRVL}$              | DRVL resistance                          | Sink, $V_{DRVL-PGND} = 0.5 \text{ V}$                                                    |         | 1.5  | 2.5  | Ω     |

|                         |                                          | DRVH-low (DRVH = 1 V) to DRVL-high<br>(DRVL = 4 V), LL = -0.05 V                         | 10      | 20   | 50   | ns    |

| T <sub>D</sub>          | Dead time                                | DRVL-low (DRVL = 1 V) to DRVH-high<br>(DRVH = 4 V), LL = -0.05 V                         | 30      | 40   | 60   | ns    |

| INTERNAI                | BST DIODE                                | X                                                                                        |         |      |      |       |

| V <sub>FBST</sub>       | Forward voltage                          | V <sub>V5DRV-VBST</sub> , IF = 10 mA, T <sub>A</sub> = 25°C                              | 0.7     | 0.8  | 0.9  | V     |

| I <sub>VBSTLK</sub>     | VBST leakage current                     | VBST = 34 V, LL = 28 V                                                                   | · · · · | 0.0  | 1    | μA    |

|                         | SIC THRESHOLD                            |                                                                                          |         | 0.1  | •    | μ, ι  |

| 3 ¥ L 3/L 3 G           | io iiiileoiloeb                          | Wake up                                                                                  | 3.7     | 3.9  | 4.1  | V     |

| $V_{UVLO}$              | V5FILT UVLO Threshold                    | Hysteresis                                                                               | 200     | 300  | 400  | mV    |

|                         |                                          | •                                                                                        | 0.7     |      |      | V     |

|                         |                                          | EN_PSV low                                                                               | 150     | 1.0  | 1.3  |       |

|                         | EN DOVIENS 1                             |                                                                                          |         | 200  | 250  | mV    |

| $V_{EN\_PSV}$           | EN_PSV logic input voltage               | EN_PSV float (set PWM_only mode)                                                         | 1.7     | 1.95 | 2.25 | V     |

|                         |                                          | EN_PSV high (set Auto_skip mode)                                                         | 2.4     | 2.65 | 2.9  | V     |

|                         |                                          | Hysteresis                                                                               | 100     | 175  | 250  | mV    |

| I <sub>EN_PSV</sub>     | EN_PSV source current                    | EN_PSV = GND, absolute value <sup>(2)</sup>                                              |         | 1    |      | μΑ    |

<sup>(1)</sup> Design constraint, ensure actual on-time is larger than the maximum value (that is, design  $R_{TON}$  such that the minimum tolerance is 100 k $\Omega$ ).

Submit Documentation Feedback

<sup>(2)</sup> Ensured by design. Not production tested.

# **Electrical Characteristics (continued)**

over operating free-air temperature range (unless otherwise noted)

|                     | PARAMETER                                    | TEST CONDITIONS                                                                                         | MIN   | TYP   | MAX   | UNIT   |

|---------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------|-------|-------|-------|--------|

| POWERG              | OOD COMPARATOR                               |                                                                                                         |       |       |       |        |

|                     |                                              | PG in from lower (PGOOD goes high)                                                                      | 92.5% | 95%   | 97.5% |        |

| .,                  | DO through ald                               | PG low hysteresis (PGOOD goes low)                                                                      | -4%   | -5.5% | -7%   |        |

| $V_{THPG}$          | PG threshold                                 | PG in from higher (PGOOD goes high)                                                                     | 102%  | 105%  | 107%  |        |

|                     |                                              | PG high hysteresis (PGOOD goes low)                                                                     | 4%    | 5.5%  | 7%    | ·      |

| I <sub>PGMAX</sub>  | PG sink current                              | PGOOD = 0.5 V                                                                                           | 2.5   | 7.5   |       | mA     |

| T <sub>PGDEL</sub>  | PG delay                                     | Delay for PGOOD in                                                                                      | 45    | 63    | 85    | μs     |

| CURREN              | T SENSE                                      |                                                                                                         |       |       | ·     |        |

| I <sub>TRIP</sub>   | TRIP source current                          | $V_{TRIP} < 0.3 \text{ V}, T_A = 25^{\circ}\text{C}$                                                    | 9     | 10    | 11    | μA     |

| T <sub>CITRIP</sub> | ITRIP temperature coefffecient               | On the basis of 25°C                                                                                    |       | 4500  |       | ppm/°C |

| $V_{Rtrip}$         | Current limit threshold range setting range  | V <sub>TRIP-GND</sub> voltage <sup>(2)</sup> , all temperatures                                         | 30    |       | 200   | mV     |

| $V_{OCLoff}$        | Overcurrent limit comparator offset          | (V <sub>TRIP-GND</sub> -V <sub>PGND-LL</sub> ) voltage V <sub>TRIP-GND</sub> = 60 mV                    | -10   | 0     | 10    | mV     |

| $V_{UCLoff}$        | Negative overcurrent limit comparator offset | $(V_{TRIP\text{-}GND}\text{-}V_{LL\text{-}PGND})$ voltage $V_{TRIP\text{-}GND}$ = 60 mV, EN_PSV = float | -9.5  | 0.5   | 10.5  | mV     |

| V <sub>ZCoff</sub>  | Zero crossing comparator offset              | V <sub>PGND-LL</sub> voltage, EN_PSV = 3.3 V                                                            | -9.5  | 0.5   | 10.5  | mV     |

| UNDERV              | OLTAGE AND OVERVOLTAGE PR                    | OTECTION                                                                                                |       |       |       |        |

| V <sub>OVP</sub>    | VFB OVP trip threshold                       | OVP detect                                                                                              | 111%  | 115%  | 119%  |        |

| T <sub>OVPDEL</sub> | VFB OVP propagation delay                    | See (2)                                                                                                 |       | 1.5   |       | μs     |

|                     | VED LIVE to the selected                     | UVP detect                                                                                              | 65%   | 70%   | 75%   | ·      |

| $V_{UVP}$           | VFB UVP trip threshold                       | Hysteresis                                                                                              |       | 10%   |       | ·      |

| T <sub>UVPDEL</sub> | VFB UVP delay                                |                                                                                                         | 22    | 32    | 42    | μs     |

| T <sub>UVPEN</sub>  | UVP enable delay                             | After 1.7 x T <sub>SS</sub> , UVP protection engaged                                                    | 1.4   | 2     | 2.6   | ms     |

|                     | L SHUTDOWN                                   |                                                                                                         |       |       |       |        |

| <b>-</b>            | The area of about decree there of the        | Shutdown temperature <sup>(2)</sup>                                                                     |       | 160   |       |        |

| T <sub>SDN</sub>    | Thermal shutdown threshold                   | Hysteresis <sup>(2)</sup>                                                                               |       | 12    |       | °C     |

Product Folder Links: TPS51117

Copyright © 2005–2015, Texas Instruments Incorporated

## 6.4 Typical Characteristics

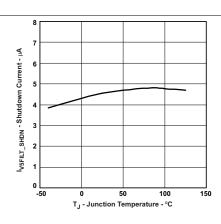

Figure 2. V5FILT Shutdown Current vs Junction Temperature

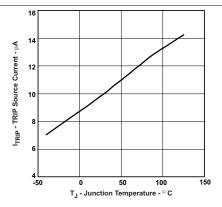

Figure 3. Trip Current vs Junction Temperature

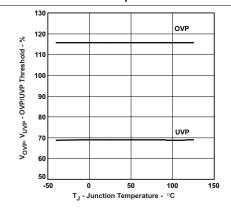

Figure 4. OVP/UVP Threshold vs Junction Temperature

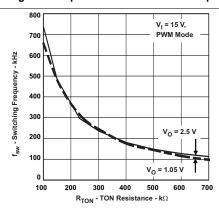

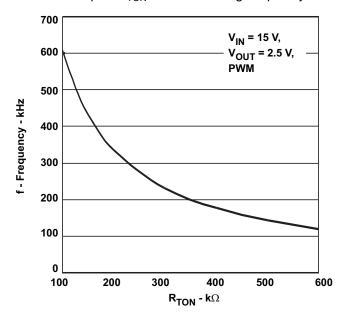

Figure 5. Measured Switching Frequency vs Ton Resistance

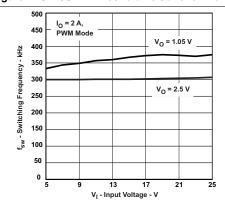

Figure 6. Switching Frequency vs Input Voltage

Copyright © 2005–2015, Texas Instruments Incorporated

Submit Documentation Feedback

## **Typical Characteristics (continued)**

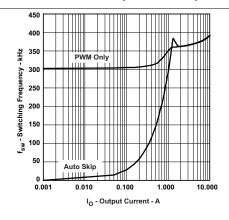

Figure 7. Switching Frequency vs Output Current (1.05 V)

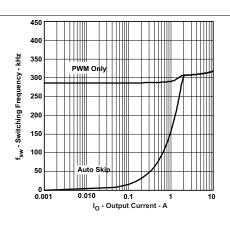

Figure 8. Switching Frequency vs Output Current (2.5 V)

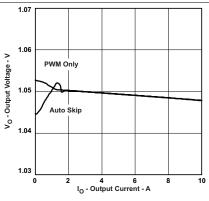

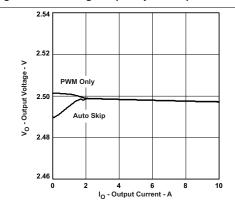

Figure 9. 1.05-V Output Voltage vs Output Current

Figure 10. 2.5-V Output Voltage vs Output Current

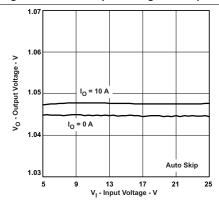

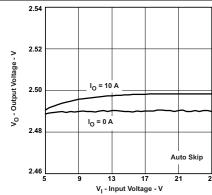

Figure 11. 1.05-V Output Voltage vs Input Voltage

Figure 12. 2.5-V Output Voltage vs Input Voltage

## **Typical Characteristics (continued)**

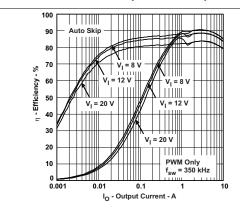

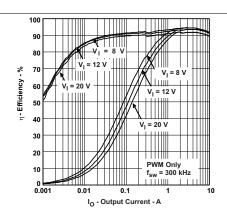

Figure 13. 1.05-V Efficiency vs Output Current

Figure 14. 2.5-V Efficiency vs Output Current

Figure 15. 1.05-V Load Transient Response

Figure 16. 2.5-V Load Transient Response

Figure 17. Mode Transition Auto-Skip to PWM

Figure 18. Mode Transition PWM to Auto-Skip

## 7 Detailed Description

#### 7.1 Overview

The TPS51117 is a synchronous buck controller for POL voltage regulation in notebook PC applications. The controller is dedicated for the operation of the Adaptive On-Time D-CAP mode. This mode provides ease-of-use, low external component count, and fast transient response. Auto-skip mode for high efficiency down to the milliampere load range, or PWM-only mode for low-noise operation is selectable.

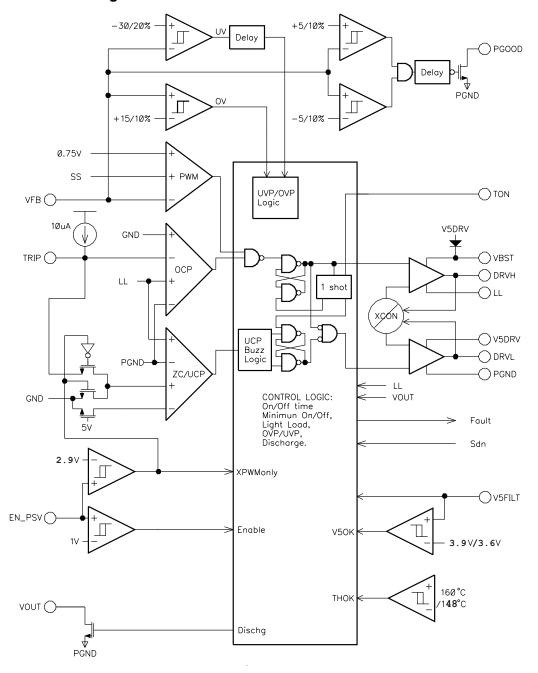

## 7.2 Functional Block Diagram

Submit Documentation Feedback

Copyright © 2005–2015, Texas Instruments Incorporated

#### 7.3 Feature Description

## 7.3.1 PWM Frequency and Adaptive On-Time Control

The TPS51117 employs an adaptive on-time control scheme and does not have a dedicated oscillator onboard. However, the device emulates a constant frequency by feed-forwarding the input and output voltages into the ontime one-shot timer. The ON time is controlled inverse proportional to the input voltage, and proportional to the output voltage, so that the duty ratio is kept as  $V_{OUT}/V_{IN}$  technically with the same cycle time. Equation 1 shows a simplified calculation of the ON time.

$$T_{ON} = 19 \times 10^{-12} \times R_{TON} \left( \frac{(2/3)V_{OUT} + 100 \text{ mV}}{V_{IN}} \right) + 50 \text{ ns}$$

(1)

Here,  $R_{TON}$  is the external resistor connected from TON pin to the LL node. In the equation, 19 pF represents the internal timing capacitor with some typical parasitic capacitance at the TON pin. Also, 50 ns is the turnoff delay time contributed by the internal circuit and that of the high-side MOSFET. Although this equation provides a good approximation with which to begin, the accuracy depends on each design and selection of the high-side MOSFET. Figure 19 shows the relationship of  $R_{TON}$  to the switching frequency.

Figure 19. Switching Frequency vs R<sub>TON</sub>

The TPS51117 does not have a pin connected to VIN, but the input voltage information comes from the switch node (LL node) during the ON-state. An advantage of LL monitoring is that the loss in the high-side NFET is now a part of the ON-time calculation, thereby making the frequency more stable with load.

Another consideration about frequency is jitter. Jitter may be caused by many reasons, but the constant on-time D-CAP mode scheme has some amount of inherent jitter. Because the output voltage ripple height is in the range of a couple of tens of millivolts. A millivolt order of noise on the feedback signal can affect the frequency by a few to ten percent. This is normal operation and has little harm to the power supply performance.

#### 7.3.2 Low-Side Driver

The low-side driver is designed to drive high-current, low  $R_{DS(on)}$  N-channel MOSFETs. The drive capability is represented by its internal resistance, which is 5  $\Omega$  for V5DRV to DRVL and 1.5  $\Omega$  for DRVL to PGND. A dead time to prevent shoot-through is internally generated between high-side MOSFET off to low-side MOSFET on, and low-side MOSFET off to high-side MOSFET on. A 5-V bias voltage is delivered from V5DRV supply. The average drive current is calculated by the FET gate charge at  $V_{gs} = 5$  V times the switching frequency. The instantaneous drive current is supplied by an input capacitor connected between V5DRV and GND.

## **Feature Description (continued)**

#### 7.3.3 High-Side Driver

The high-side driver is designed to drive high-current, low  $R_{DS(on)}$  N-channel MOSFET(s). When configured as a floating driver, 5-V bias voltage is delivered from V5DRV supply. An internal PN diode is connected between V5DRV to VBST. The designer can add an external Schottky diode if forward drop is critical to drive the high-side NFET or to achieve the last 1% efficiency improvement. The average drive current is also estimated by the gate charge at  $V_{gs} = 5$  V times the switching frequency. The instantaneous drive current is supplied by the flying capacitor between the VBST pin and LL pin. The drive capability is represented by its internal resistance, which is 5  $\Omega$  for VBST to DRVH and 1.5  $\Omega$  for DRVH to LL.

#### 7.3.4 Soft-Start

The TPS51117 has an internal, 1.2-ms, voltage servo soft-start with overcurrent limit. When the EN\_PSV pin becomes high, an internal DAC begins ramping up the reference voltage to the error amplifier. Smooth control of the output voltage is maintained during start-up.

#### 7.3.5 Powergood

The TPS51117 has powergood output. PGOOD is an open-drain 7.5-mA pulldown output. This pin should be typically connected to a 5-V power supply node through a  $100\text{-k}\Omega$  resistor. The powergood function is activated after the soft start has finished. If the output voltage becomes within  $\pm 5\%$  of the target value, internal comparators detect the power good state and the powergood signal becomes high after a 64- $\mu$ s internal delay. If the output voltage goes outside  $\pm 10\%$  of the target value, the powergood signal becomes low immediately.

## 7.3.6 Output Discharge Control (Soft-Stop)

The TPS51117 discharges output when EN\_PSV is low or the converter is in a fault condition (UVP, OVP, UVLO, or thermal shutdown). The TPS51117 discharges output using an internal  $20-\Omega$  MOSFET, which is connected to VOUT and PGND. The discharge time-constant is a function of the output capacitance and resistance of the discharge transistor.

#### 7.3.7 Overcurrent Limit

The TPS51117 has cycle-by-cycle overcurrent limiting control. Inductor current is monitored during the OFF-state and the controller keeps the OFF-state when inductor current is larger than the overcurrent trip level. To provide both good accuracy and a cost-effective solution, the TPS51117 supports temperature compensated MOSFET  $R_{DS(on)}$  sensing. The TRIP pin should be connected to GND through the trip voltage setting resistor,  $R_{TRIP}$ . The TRIP terminal sources 10- $\mu$ A  $I_{TRIP}$  current, and the trip level is set to the OCL trip voltage,  $V_{TRIP}$  as in the following equation.

$$V_{TRIP} (mV) = R_{TRIP} (k\Omega) \times 10 (\mu A)$$

(2)

Inductor current is monitored by the voltage between the PGND pin and the LL pin so the LL pin should be connected to the drain terminal of the low-side MOSFET.  $I_{TRIP}$  has 4500 ppm/°C temperature coefficient to compensate the temperature dependency of the  $R_{DS(on)}$ . PGND is used as the positive current sensing node so PGND should be connected to the source terminal of the bottom MOSFET.

As the comparison is done during the OFF-state,  $V_{TRIP}$  sets the valley level of the inductor current. Thus, the load current at overcurrent threshold,  $I_{ocp}$ , can be calculated as follows;

$$I_{\text{ocp}} = V_{\text{TRIP}} / R_{\text{DS(on)}} + I_{\text{RIPPLE}} / 2 = \frac{V_{\text{TRIP}}}{R_{\text{DS(on)}}} + \frac{1}{2 \times L \times f} \times \frac{\left(V_{\text{IN}} - V_{\text{OUT}}\right) \times V_{\text{OUT}}}{V_{\text{IN}}}$$

(3)

In an overcurrent condition, the current to the load exceeds the current to the output capacitor, thus the output voltage tends to fall. Eventually, the output voltage crosses the undervoltage protection threshold and shutdown.

## **Feature Description (continued)**

#### 7.3.8 Negative Overcurrent Limit (PWM-Only Mode)

The TPS51117 also supports cycle-by-cycle negative overcurrent limiting in PWM-only mode. The overcurrent limit is set to be negative but is the same absolute value as the positive overcurrent limit. If output voltage continues to rise, the bottom MOSFET stays on, thus inductor current is reduced and reverses direction after it reaches zero. When there is too much negative current in the inductor, the bottom MOSFET is turned off and the current flows to VIN through the body diode of the top MOSFET. Because this protection reduces current to discharge the output capacitor, output voltage tends to rise, eventually hitting the overvoltage protection threshold and shutdown. To prevent false OVP from triggering, the bottom MOSFET is turned on again 400 ns after it is turned off. If the device hits the negative overcurrent threshold again before output voltage is discharged to the target level, the bottom MOSFET is turned off and the process repeats, which is called NOCL Buzz. The device ensures maximum allowable discharge capability when output voltage continues to rise. On the other hand, if the output voltage is discharged to the target level before the NOCL threshold is reached, the bottom MOSFET is turned off, the top MOSFET is then turned on, and the device resumes normal operation.

#### 7.3.9 Overvoltage Protection

The TPS51117 monitors a resistor divided feedback voltage to detect overvoltage and undervoltage condition. When the feedback voltage becomes higher than 115% of the target value, the top MOSFET is turned off and the bottom MOSFET is turned on immediately. The output is also discharged by the internal  $20-\Omega$  transistor. Also, the TPS51117 monitors VOUT terminal voltage directly and if it becomes greater than 5.75 V, it turns off the top MOSFET driver.

#### 7.3.10 Undervoltage Protection

When the feedback voltage becomes lower than 70% of the target value, the UVP comparator output goes high and an internal UVP delay counter begins counting. After 32 µs, the TPS51117 latches off the high-side and lowside MOSFETs and discharges the output with the internal 20-Ω transistor. This function is enabled after 2 ms from when EN\_PSV is brought high, that is, UVP is disabled during start-up.

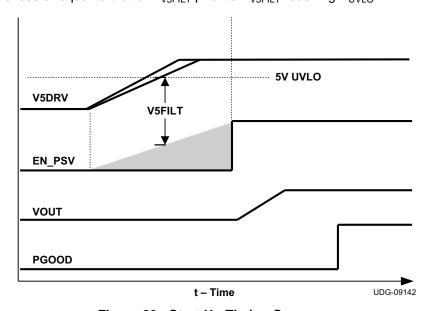

#### 7.3.11 Start-Up Sequence

Referring to Figure 20 which shows the timing sequence, to ensure the proper start-up of the TPS51117, always ensure that V<sub>EN PSV</sub> is less or equal to that of V<sub>V5FILT</sub> prior to V<sub>V5FILT</sub> reaching V<sub>UVLO</sub>.

Figure 20. Start-Up Timing Sequence

Copyright © 2005-2015, Texas Instruments Incorporated

## **Feature Description (continued)**

#### 7.3.12 UVLO Protection

The TPS51117 has V5FILT undervoltage lockout protection (UVLO). When the V5FILT voltage is lower than the UVLO threshold voltage, the TPS51117 is shut off. This is a nonlatched protection.

#### 7.3.13 Thermal Shutdown

The TPS51117 monitors the temperature of itself. If the temperature exceeds the threshold value (typically 160°C), the TPS51117 shuts itself off. Both top and bottom gate drivers are tied low with output discharged through the VOUT terminal. This is also a nonlatched protection. The device recovers once the temperature has decreased approximately 12°C.

#### 7.4 Device Functional Modes

## 7.4.1 PWM Operation

The main control loop of the TPS51117 is designed as an adaptive on-time pulse width modulation (PWM) controller. It supports proprietary D-CAP Mode that uses an internal compensation circuit and is suitable for minimal external component count configuration when an appropriate amount of ESR at the output capacitor(s) is allowed. Basic operation of D-CAP Mode can be described as follows.

At the beginning of each cycle, the synchronous high-side MOSFET is turned on, or becomes ON-state. This MOSFET is turned off, or becomes OFF-state, after the internal one-shot timer expires. This one-shot is determined by  $V_{IN}$  and  $V_{OUT}$  to keep the frequency fairly constant over the input voltage range at steady-state, hence it is called adaptive on-time control or fixed frequency emulated on-time control (see *PWM Frequency and Adaptive On-Time Control*). The MOSFET is turned on again when both feedback information, monitored at  $V_{FB}$  voltage, indicates insufficient output voltage and inductor current information indicates below the overcurrent limit. Repeating the operation in this manner, the controller regulates the output voltage. The synchronous low-side or *rectifying* MOSFET is turned on each OFF-state to keep the conduction loss to a minimum.

The TPS51117 supports selectable PWM-only and auto-skip operation modes. If EN\_PSV is grounded, the switching regulator is disabled. If the EN\_PSV pin is connected to 3.3 V or 5 V, the regulator is enabled with auto-skip mode selected. The rectifying MOSFET is turned off when inductor current information detects zero level. This enables a seamless transition to reduced frequency operation during a light-load condition so that high efficiency is maintained over a broad range of load currents. If the EN\_PSV pin is floated, it is internally pulled up to 1.95 V, and the regulator is enabled with PWM-only mode selected. The rectifying MOSFET is not turned off when inductor current reaches zero. The converter runs forced continuous conduction mode for the entire load range. System designers may want to use this mode to avoid a certain frequency during a light-load condition but with the cost of low efficiency. However, be aware the output has the capability to both source and sink current in this mode. If the output terminal is connected to a voltage source higher than the target of the regulator, the converter sinks current from the output and boosts the charge into the input capacitor. This may cause unexpected high voltage at VIN and may damage the power FETs.

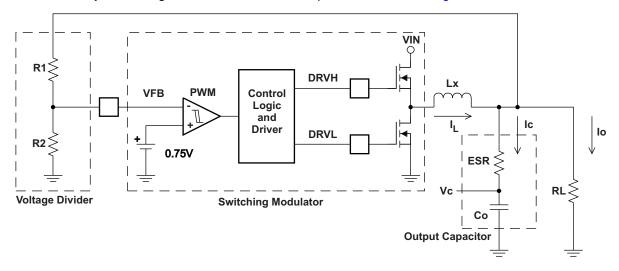

DC output voltage can be set by the external resistor divider as follows (refer to Figure 21, Figure 24, and Figure 25).

$$V_{OUT} = \left(1 + \frac{R_1}{R_2}\right) \times 0.75 V \tag{4}$$

## 7.4.2 Light-Load Condition With Auto-Skip Function

If auto-skip mode is selected, the TPS51117 automatically reduces the switching frequency during a light-load condition to maintain high efficiency. This reduction of frequency is achieved smoothly and without an increase of V<sub>out</sub> ripple or load regulation. Detailed operation is described as follows. As the output current decreases from a heavy load condition, the inductor current is also reduced and eventually comes to the point that its valley touches zero current, which is the boundary between continuous conduction and discontinuous conduction modes. The rectifying MOSFET is turned off when this zero inductor current is detected. Because the output voltage is still higher than the reference at this moment, both high-side and low-side MOSFETs are turned off and wait for the next cycle. As the load current decreases further, the converter runs in discontinuous conduction

(5)

## **Device Functional Modes (continued)**

mode, taking longer time to discharge the output capacitor below the reference voltage. The ON time is kept the same as during the heavy load condition. In reverse, when the output current increases from a light load to a heavy load, the switching frequency increases to the preset value as the inductor current reaches to the continuous conduction. The transition load point to light-load operation, I<sub>OUT(LL)</sub> (that is, the threshold between continuous and discontinuous conduction mode), can be calculated as follows:

$$I_{OUT(LL)} = \frac{1}{2 \times L \times f_{SW}} \times \frac{\left(V_{IN} - V_{OUT}\right) \times V_{OUT}}{V_{IN}}$$

where

Switching frequency versus output current in the light-load condition is a function of L,  $f_{sw}$ ,  $V_{IN}$  and  $V_{OUT}$ , but it decreases almost proportional to the output current from the  $I_{OUT(LL)}$  given in Equation 5. For example, it is about 60 kHz at  $I_{OUT(LL)}/5$  if the PWM switching frequency is 300 kHz.

## 8 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

## 8.1 Application Information

The TPS51117 is a cost-effective, synchronous buck controller for POL voltage regulation in notebook PC applications. The controller is dedicated for Adaptive On-Time D-CAP Mode operation. Use the following design procedure to select component values for each device.

## 8.2 Typical Application

A buck converter system using D-CAP Mode can be simplified as shown in Figure 21.

Figure 21. Simplified Diagram of the Modulator

#### 8.2.1 Design Requirements

For this design example, use Table 1 as the input parameters.

**Table 1. Design Parameters**

| DESIGN PARAMETER      | EXAMPLE VALUE |

|-----------------------|---------------|

| Input Voltage Range   | 1.8 V to 28 V |

| Output Voltage        | 1.05 V        |

| Output Current Rating | 10 A          |

Copyright © 2005–2015, Texas Instruments Incorporated Product Folder Links: *TPS51117*

#### 8.2.2 Detailed Design Procedure

#### 8.2.2.1 D-CAP Mode Operation

The VFB voltage is compared with the internal reference voltage after the divider resistors. The PWM comparator determines the timing to turn on the top MOSFET. The gain and speed of the comparator is high enough to keep the voltage at the beginning of each on cycle (or the end of off cycle) substantially constant. The DC output voltage may have line regulation due to ripple amplitude that slightly increases as the input voltage increases.

For loop stability, the 0 dB frequency,  $f_0$ , defined in Equation 6 must be lower than 1/4 of the switching frequency.

$$f_{O} = \frac{1}{2\Pi \times \mathsf{ESR} \times \mathsf{Co}} \le \frac{f_{\mathsf{SW}}}{4} \tag{6}$$

As  $f_0$  is determined solely by the output capacitor characteristics, loop stability of D-CAP Mode is determined by capacitor chemistry. For example, specialty polymer capacitors (SP-CAP) have Co in the order of several 100  $\mu$ F and ESR in range of 10 m $\Omega$ . These values make  $f_0$  in the order of 100 kHz or less and the loop is stable. However, ceramic capacitors have  $f_0$  at more than 700 kHz, which is not suitable for this operational mode.

Although D-CAP Mode provides many advantages such as ease-of-use, minimum external component configuration, and extremely short response time, due to not employing an error amplifier in the loop, a sufficient feedback signal must be provided by an external circuit to reduce the jitter level. The required signal level is approximately 15 mV at the comparing point. This generates  $V_{ripple} = (V_{OUT}/0.75) \times 15$  mV at the output node. The output capacitor ESR should meet this requirement.

The external component selection is simple in D-CAP Mode:

#### 1. Determine the value of R1 and R2

The recommended R2 value is 10 k $\Omega$  to 100 k $\Omega$ . Calculate R1 by Equation 7.

$$R1 = \frac{\left(V_{OUT}^{-0.75}\right)}{0.75} \times R2 \tag{7}$$

#### Choose R<sub>TON</sub>

Switching frequency is usually determined by the overall view of the DC-DC converter design of: size, efficiency or cost, and mostly dictated by external component constraints such as the size of inductor and/or output capacitor. When an extremely low or high duty factor is expected, the minimum on-time or off-time also must be considered to satisfy the required duty factor. Once the switching frequency is decided,  $R_{TON}$  can be determined by Equation 8 and Equation 9,

$$T_{ON(max)} = \frac{1}{f} \times \frac{V_{OUT}}{V_{IN(min)}}$$

(8)

$$R_{TON} = \frac{3}{2} \times \frac{\left(T_{ON(max)}^{-50ns}\right)}{19 \times 10^{-12}} \times \frac{V_{IN(min)}}{\left(V_{OUT} + 150 \,\text{mV}\right)} \left[\Omega\right]$$

(9)

#### 3. Choose inductor

A good starting point inductance value is where the ripple current is approximately 1/4 to 1/2 of the maximum output current.

$$L_{IND} = \frac{1}{I_{IND(ripple)} \times f} \times \frac{\left(V_{IN(max)} - V_{OUT}\right) \times V_{OUT}}{V_{IN(max)}} = \frac{3}{I_{OUT(max)} \times f} \times \frac{\left(V_{IN(max)} - V_{OUT}\right) \times V_{OUT}}{V_{IN(max)}}$$

(10)

For applications that require fast transient response with minimum  $V_{OUT}$  overshoot, consider a smaller inductance than above. The cost of a small inductance value is higher steady-state ripple, larger line regulation, and higher switching loss.

The inductor also needs to have low DCR to achieve good efficiency, as well as enough room above peak inductor current before saturation. The peak inductor current can be estimated in Equation 11.

$$I_{\text{IND(peak)}} = \frac{V_{\text{TRIP}}}{R_{\text{DS(on)}}} + \frac{1}{L \times f} \times \frac{\left(V_{\text{IN(max)}} - V_{\text{OUT}}\right) \times V_{\text{OUT}}}{V_{\text{IN(max)}}}$$

(11)

#### 4. Choose output capacitor(s)

Organic semiconductor capacitor(s) or specialty polymer capacitor(s) are recommended. Determine ESR to meet the required ripple voltage above. A quick approximation is shown in Equation 12.

$$ESR = \frac{V_{OUT} \times 0.015}{I_{ripple} \times 0.75} \approx \frac{V_{OUT}}{I_{OUT(max)}} \times 60 [m\Omega]$$

(12)

#### Choose MOSFETs

Loss-less current sensing and overcurrent protection of the TPS51117 is determined by  $R_{DS(on)}$  of the low-side MOSFET. So,  $R_{DS(on)}$  times the inductor current value at the overcurrent point should be in the range of 30 mV to 200 mV for the entire operational temperature range. Assuming a 20% guard band,  $R_{DS(on)}$  in Equation 13 should satisfy the full temperature range.

$$\frac{30\,\text{mV}}{1.2\times I_{OUT(max)} - 0.5\times I_{ripple}} \leq R_{DS(on)} \leq \frac{200\,\text{mV}}{1.2\times I_{OUT(max)} - 0.5\times I_{ripple}} \tag{13}$$

#### 6. Choose R<sub>trin</sub>

Once the low-side FET is decided, select an appropriate  $R_{trip}$  value that provides  $V_{trip}$  equal to  $R_{DS(on)}$  times  $I_{peak}$ .

#### 7. LPF for V5FILT

To reject high-frequency noise and also secure safe start-up of the internal reference circuit, apply 1  $\mu$ F of MLCC closely at the V5FILT pin with a 300- $\Omega$  resistor to create a LPF between +5-V supply and the pin.

#### 8. VBST capacitor, VBST diode

Apply 0.1-µF MLCC between VBST and the LL node as the flying capacitor for the high-side FET driver. The TPS51117 has its own boost diode onboard between V5DRV and VBST. This is a PN junction diode and strong enough for most typical applications. However, in case efficiency has priority over cost, the designer may add a Schottky diode externally to improve gate drive voltage of the high-side FET. A Schottky diode has a higher leakage current, especially at high temperature, than a PN junction diode. A low-leakage diode should be selected in order to maintain VBST voltage during low-frequency operation in skip mode.

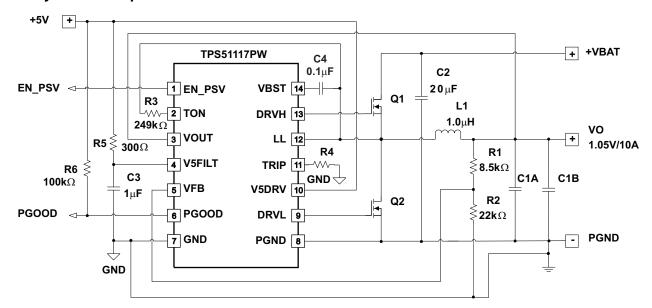

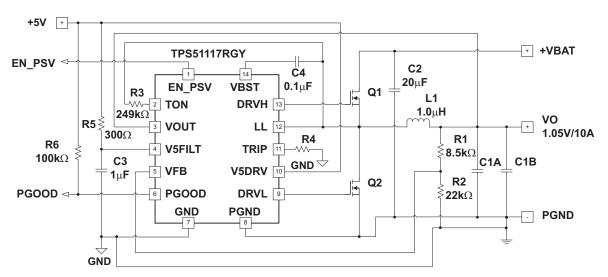

**Table 2. Typical Application Circuit Components**

| SYMBOL   | SPECIFICATION        | MANUFACTURER            | PART NUMBER             |

|----------|----------------------|-------------------------|-------------------------|

| C1A, C1B | 470 μF, 2.5 V, 12 mΩ | SANYO                   | 2R5TPE470MC             |

| C2       | 10 μF, 25 V, 2 pcs   | Murata                  | GRM31CR61E106KA12B      |

| L1       | 1.0 μH               | Vishay, Toko            | IHLP-5050, FDA1254-1R0M |

| Q1       | 30 V, 13 mΩ          | International Rectifier | IRF7821                 |

| Q2       | 30 V, 5.8 mΩ         | International Rectifier | IRF8113                 |

| R4       | 8.06 kΩ              | _                       | Std                     |

Product Folder Links: TPS51117

Copyright © 2005-2015, Texas Instruments Incorporated

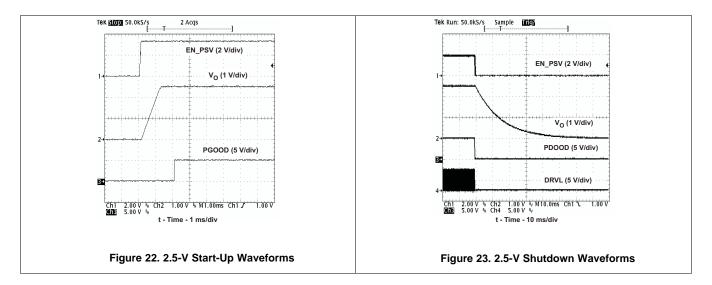

## 8.2.3 Application Curves

#### 8.3 System Examples

Figure 24. 1.05-V/10-A Application from VBAT (PW Package)

Figure 25. 1.05-V/10-A Application from VBAT (RGY Package)

Submit Documentation Feedback

## 9 Power Supply Recommendations

The devices are designed to operate at 5 V (4.5 V to 5.5 V) supply from another regulator such as the Limit TPS51120 or TPS51020. The conversion input can be either VBAT or a 5-V rail, ranging from 1.8 V to 28 V. In order to reject high-frequency noise and also secure safe start-up of the internal reference circuit, apply 1  $\mu$ F of MLCC closely at the V5FILT pin with a 300- $\Omega$  resistor to create a LPF between 5-V supply and the pin.

## 10 Layout

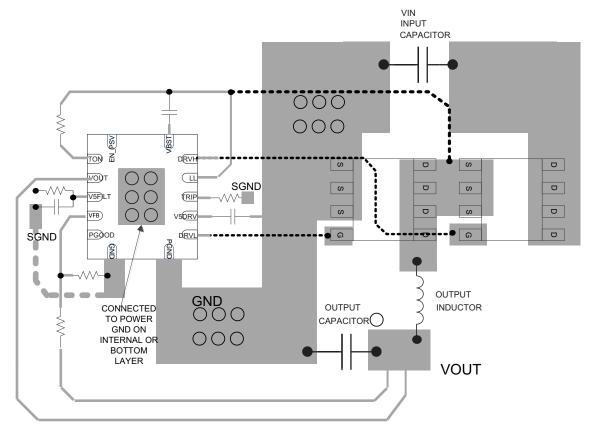

## 10.1 Layout Guidelines

Certain points must be considered before starting a layout work using the TPS51117.

- Connect the RC low-pass filter from 5-V supply to V5FILT, 300 Ω and 1 μF are recommended. Place the filter capacitor close to the device, within 12 mm (0.5 inches) if possible.

- Connect the overcurrent setting resistors from TRIP to GND close to the device, right next to the device, if

possible. The trace from TRIP to resistor and resistor to GND should avoid coupling to a high-voltage

switching node.

- The discharge path (VOUT) should have a dedicated trace to the output capacitor(s); separate from the

output voltage sensing trace, and use a 1.5-mm (60 mils) or wider trace with no loops. Make sure the

feedback current setting resistor (the resistor between VFB to GND) is tied close to the device GND. The

trace from this resistor to the VFB pin should be short and thin. Place on the component side and avoid vias

between this resistor and the device.

- Connections from the drivers to the respective gate of the high-side or the low-side MOSFET should be as short as possible to reduce stray inductance. Use a 0.65-mm (25 mils) or wider trace.

- All sensitive analog traces and components such as VOUT, VFB, GND, EN\_PSV, PGOOD, TRIP, V5FILT, and TON should be placed away from high-voltage switching nodes such as LL, DRVL, DRVH or VBST to avoid coupling. Use internal layer(s) as ground plane(s) and shield feedback trace from power traces and components.

- Gather the ground terminals of the V<sub>IN</sub> capacitor(s), V<sub>OUT</sub> capacitor(s), and the source of the low-side MOSFETs as close as possible. GND (signal ground) and PGND (power ground) should be connected strongly together near the device. The PCB trace defined as LL node, which connects to the source of the high-side MOSFET, the drain of the low-side MOSFET, and the high-voltage side of the inductor, should be as short and wide as possible.

## 10.2 Layout Example

Figure 26. Layout Recommendation

#### 10.3 Thermal Considerations

Power dissipation of the TPS51117 is mainly generated from the FET drivers. Average drive current can be estimated by gate charge,  $Q_q$ , times the switching frequency.

$$I_{G} = Q_{g} \times f_{SW} \tag{14}$$

$Q_g$  is the charge needed to charge gate capacitance up to the V5DRV voltage of 5 V. Actual values are shown on MOSFET datasheets provided by the manufacturer. Total power dissipation, therefore, to drive the top and bottom MOSFETs can be calculated by the following equation Equation 15.

$$W_{DRIVE} = V_{V5DRV} \times \left(Q_{g(top)} + Q_{g(btm)}\right) \times f_{SW}$$

(15)

This power plus a small amount of dissipation (less than 5 mW) from controller circuitry needs to be effectively dissipated from the package. Maximum power dissipation allowed for the package is calculated by:

$$W_{PKG} = \frac{T_{J(max)} - T_{A(max)}}{R_{\Theta JA}}$$

where

- T<sub>J(max)</sub> is 125°C.

- $T_{A(max)}$  is the maximum ambient temperature in the system.

- R<sub>BJA</sub> is the thermal resistance from the silicon junction to the ambient.

This thermal resistance strongly depends on board layout. The TPS51117 is assembled in a standard TSSOP package and the heat mainly moves to the board through its leads.

Product Folder Links: TPS51117

(16)

## 11 Device and Documentation Support

#### 11.1 Device Support

#### 11.1.1 Third-Party Products Disclaimer

TI'S PUBLICATION OF INFORMATION REGARDING THIRD-PARTY PRODUCTS OR SERVICES DOES NOT CONSTITUTE AN ENDORSEMENT REGARDING THE SUITABILITY OF SUCH PRODUCTS OR SERVICES OR A WARRANTY, REPRESENTATION OR ENDORSEMENT OF SUCH PRODUCTS OR SERVICES, EITHER ALONE OR IN COMBINATION WITH ANY TI PRODUCT OR SERVICE.

## 11.2 Community Resources

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E™ Online Community TI's Engineer-to-Engineer (E2E) Community. Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support** *TI's Design Support* Quickly find helpful E2E forums along with design support tools and contact information for technical support.

#### 11.3 Trademarks

D-CAP, E2E are trademarks of Texas Instruments.

All other trademarks are the property of their respective owners.

## 11.4 Electrostatic Discharge Caution

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### 11.5 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

## 12 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

www.ti.com 2-May-2025

#### PACKAGING INFORMATION

| Orderable part number | Status<br>(1) | Material type | Package   Pins  | Package qty   Carrier RoHS |     | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|---------------|---------------|-----------------|----------------------------|-----|-------------------------------|----------------------------|--------------|------------------|

| TPS51117PW            | Active        | Production    | TSSOP (PW)   14 | 90   TUBE                  | Yes | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 85    | 51117            |

| TPS51117PWR           | Active        | Production    | TSSOP (PW)   14 | 2000   LARGE T&R           | Yes | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 85    | 51117            |

| TPS51117RGYR          | Active        | Production    | VQFN (RGY)   14 | 3000   LARGE T&R           | Yes | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 85    | 51117            |

| TPS51117RGYT          | Active        | Production    | VQFN (RGY)   14 | 250   SMALL T&R            | Yes | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 85    | 51117            |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 25-Sep-2024

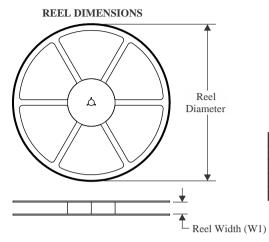

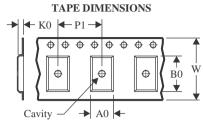

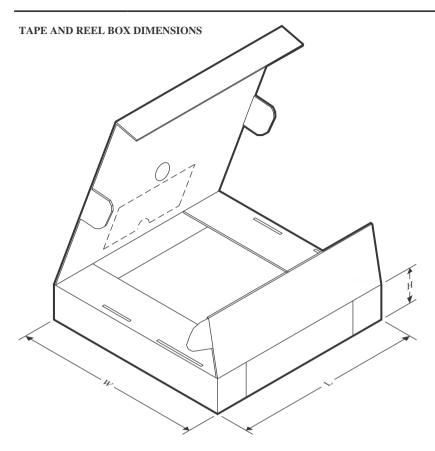

## TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

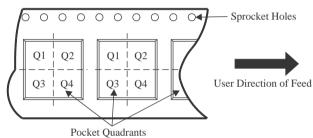

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device       | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPS51117PWR  | TSSOP           | PW                 | 14 | 2000 | 330.0                    | 12.4                     | 6.9        | 5.6        | 1.6        | 8.0        | 12.0      | Q1               |

| TPS51117RGYR | VQFN            | RGY                | 14 | 3000 | 330.0                    | 12.4                     | 3.75       | 3.75       | 1.15       | 8.0        | 12.0      | Q1               |

| TPS51117RGYR | VQFN            | RGY                | 14 | 3000 | 330.0                    | 12.4                     | 3.75       | 3.75       | 1.15       | 8.0        | 12.0      | Q1               |

| TPS51117RGYT | VQFN            | RGY                | 14 | 250  | 180.0                    | 12.4                     | 3.75       | 3.75       | 1.15       | 8.0        | 12.0      | Q1               |

www.ti.com 25-Sep-2024

#### \*All dimensions are nominal

| Device       | Package Type | Package Drawing | g Pins SPQ |      | Length (mm) | Width (mm) | Height (mm) |  |

|--------------|--------------|-----------------|------------|------|-------------|------------|-------------|--|

| TPS51117PWR  | TSSOP        | PW              | 14         | 2000 | 356.0       | 356.0      | 35.0        |  |

| TPS51117RGYR | VQFN         | RGY             | 14         | 3000 | 346.0       | 346.0      | 33.0        |  |

| TPS51117RGYR | VQFN         | RGY             | 14         | 3000 | 356.0       | 356.0      | 35.0        |  |

| TPS51117RGYT | VQFN         | RGY             | 14         | 250  | 210.0       | 185.0      | 35.0        |  |

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 25-Sep-2024

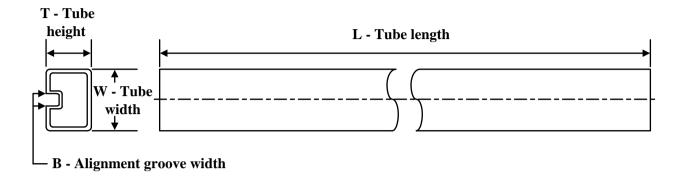

## **TUBE**

#### \*All dimensions are nominal

|   | Device     | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (µm) | B (mm) |

|---|------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| ı | TPS51117PW | PW           | TSSOP        | 14   | 90  | 530    | 10.2   | 3600   | 3.5    |

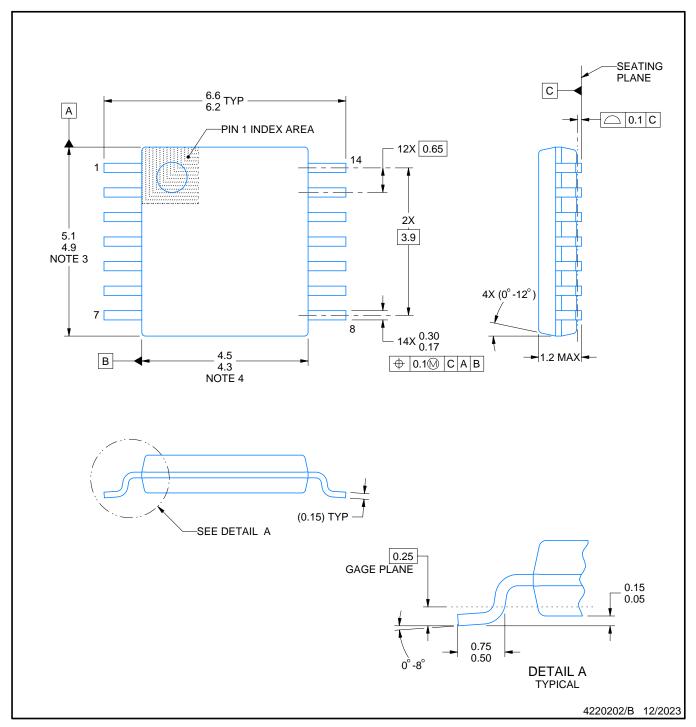

SMALL OUTLINE PACKAGE

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

- 5. Reference JEDEC registration MO-153.

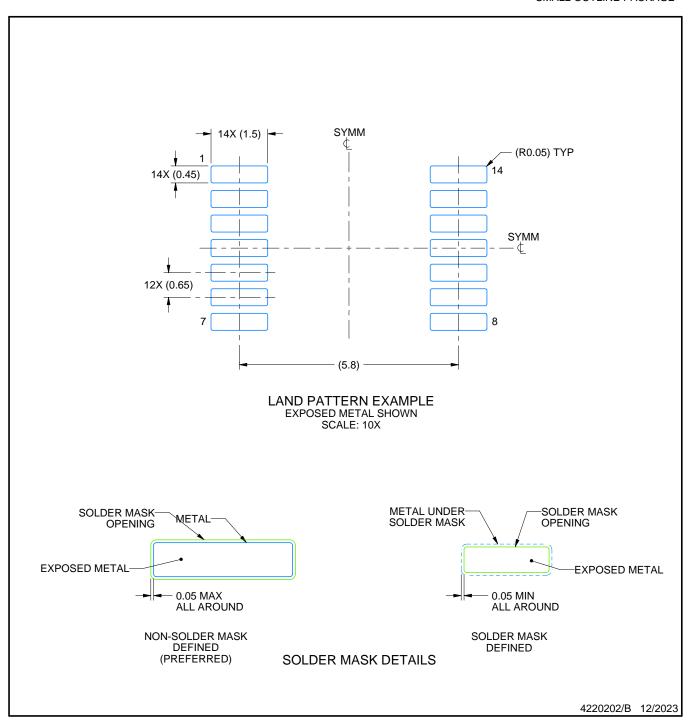

SMALL OUTLINE PACKAGE

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

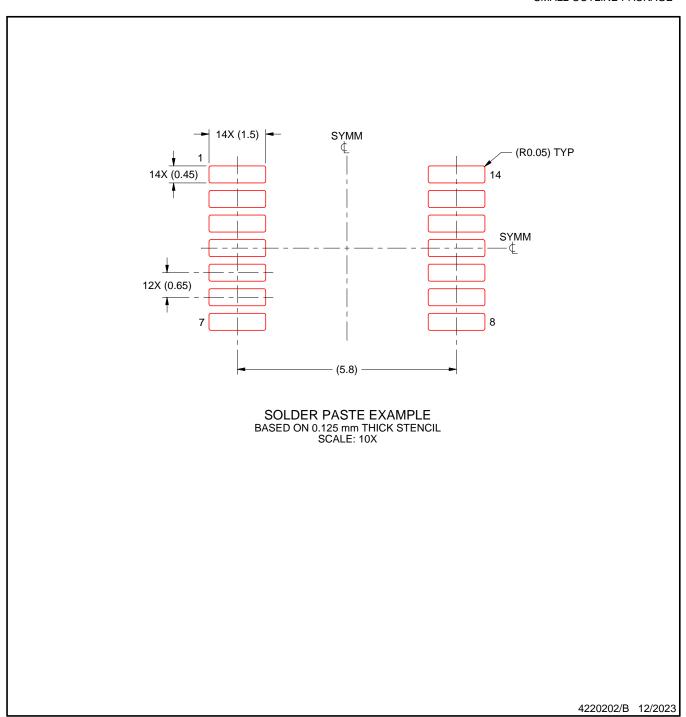

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

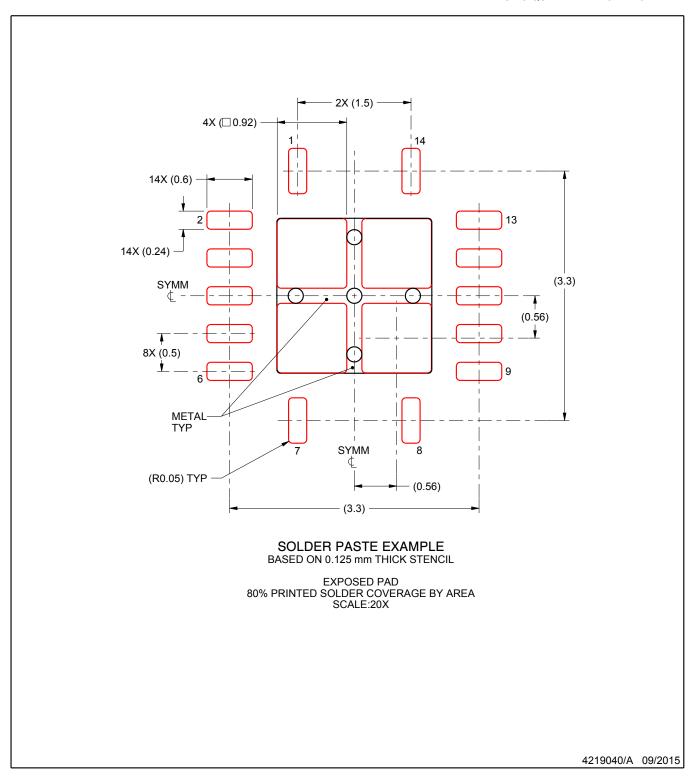

3.5 x 3.5, 0.5 mm pitch

PLASTIC QUAD FLATPACK - NO LEAD

This image is a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

INSTRUMENTS www.ti.com

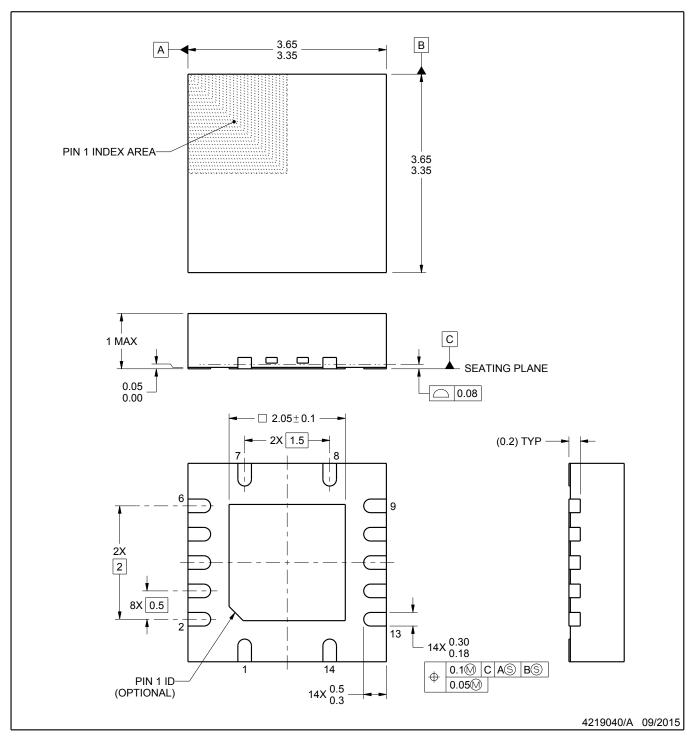

PLASTIC QUAD FLATPACK - NO LEAD

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- This drawing is subject to change without notice.

The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

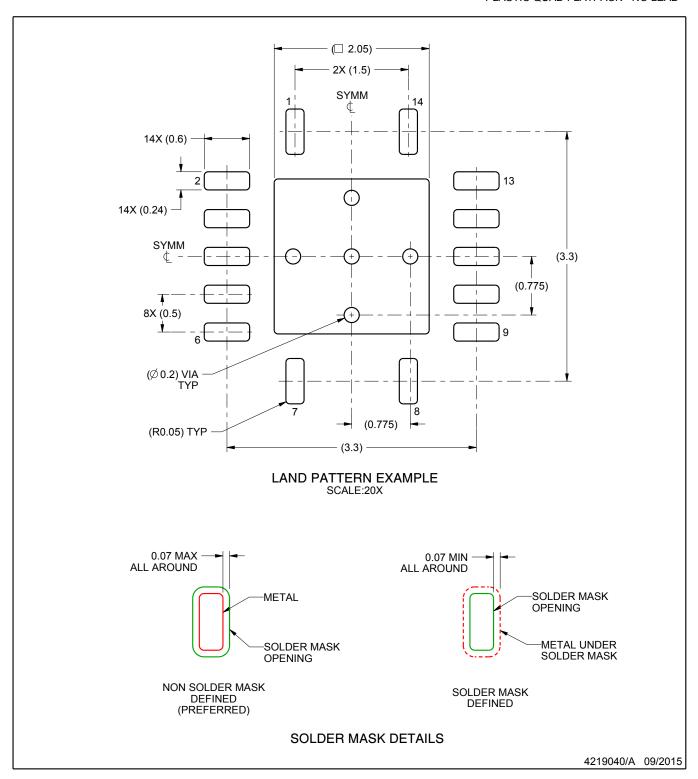

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

5. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025. Texas Instruments Incorporated