# 用于桥式传感器的 24 位模数转换器

查询样片: ADS1231

### 特性

- 针对桥式传感器的完整前端

- 内部放大器,128 增益

- 内部振荡器

- 针对桥式传感器的低侧电源开关

- 低噪声: 35nVrms

- 可选数据速率: 10SPS 或 80SPS

- 10SPS 时,同时 50Hz 和 60Hz 抑制

- 输入电磁干扰 (EMI) 滤波器

- 针对比例式测量的高达 5V 的外部电压基准

- 简单、引脚驱动控制

- 两线制串行数字接口

- 电源范围: 3V 至 5.3V

- 封装: 小外形尺寸集成电路 (SOIC)-16

- 温度范围: -40°C 至 +85°C

### 应用范围

- 衡器

- 应力计

- 测压元件

- 工业过程控制

### 说明

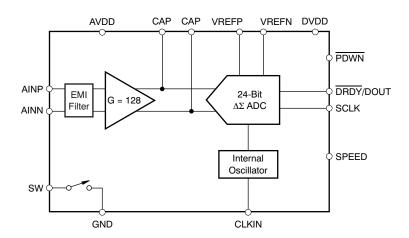

ADS1231 是一款精密 24 位模数转换器 (ADC)。 借助于板载低噪声放大器和振荡器,精密型三阶 24 位 ΔΣ 调制器以及桥式电源开关,ADS1231 为包括衡器、应力计和测压元件在内的桥式传感器应用提供一个完整的前端解决方案。

此噪声放大器具有 128 的增益,从而支持 ±19.5mV 的 满量程差分输入。此 ΔΣ ADC 具有 24 位分辨率,并 且包含一个三阶调制器和四阶数字滤波器。 支持两个 数据速率: 10SPS(具有 50Hz 和 60Hz 抑制)以及 80SPS。 ADS1231 可被置于低功耗待机模式,或者在 断电模式中完全关闭。

ADS1231 由专用引脚控制,没有编程用的数字寄存器。数据通过直接接至 MSP430 或其它微控制器的一个易于隔离的串行接口输出。

ADS1231 采用小外形尺寸 (SO)-16 封装,额定温度范围 -40°C 至 +85°C。

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

All trademarks are the property of their respective owners.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

### ORDERING INFORMATION

For the most current package and ordering information, see the Package Option Addendum at the end of this document, or visit the device product folder at www.ti.com.

### **ABSOLUTE MAXIMUM RATINGS**(1)

Over operating free-air temperature range, unless otherwise noted.

|                             |                                                                           | ADS1231            | UNIT |

|-----------------------------|---------------------------------------------------------------------------|--------------------|------|

| AVDD to GND                 |                                                                           | -0.3 to +6         | V    |

| DVDD to GND                 |                                                                           | -0.3 to +6         | V    |

| Innut ourrent               |                                                                           | 100, momentary     | mA   |

| Input current               |                                                                           | 10, continuous     | mA   |

| Analog input voltage to GND |                                                                           | -0.3 to AVDD + 0.3 | V    |

| Digital input vo            | oltage to GND                                                             | -0.3 to DVDD + 0.3 |      |

| ESD <sup>(2)</sup>          | Human body model (HBM) JEDEC standard 22, test method A114-C.01, all pins | ±2000              | V    |

| E2D/-/                      | Charged device model (CDM) JEDEC standard 22, test method C101, all pins  | ±500               | V    |

| Maximum junc                | tion temperature                                                          | +150               | °C   |

| Operating temp              | perature range                                                            | -40 to +85         |      |

| Storage tempe               | erature range                                                             | -60 to +150        | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### THERMAL INFORMATION

|                  |                                              | ADS1231  |         |

|------------------|----------------------------------------------|----------|---------|

|                  | THERMAL METRIC <sup>(1)</sup>                | SOIC (D) | UNITS   |

|                  |                                              | 16 PINS  |         |

| $\theta_{JA}$    | Junction-to-ambient thermal resistance       | 79.5     |         |

| $\theta_{JCtop}$ | Junction-to-case (top) thermal resistance    | 37.5     |         |

| $\theta_{JB}$    | Junction-to-board thermal resistance         | 37.1     | °C/W    |

| ΨЈТ              | Junction-to-top characterization parameter   | 5.6      | - °C/VV |

| ΨЈВ              | Junction-to-board characterization parameter | 36.7     |         |

| $\theta_{JCbot}$ | Junction-to-case (bottom) thermal resistance | n/a      |         |

(1) 有关传统和全新热度量的更多信息,请参阅 IC 封装热度量 应用报告 (文献号: ZHCA543)。

<sup>(2)</sup> CAUTION: ESD sensitive device. Precaution should be used when handling the device in order to prevent permanent damage.

### **ELECTRICAL CHARACTERISTICS**

Minimum/maximum limit specifications apply from  $-40^{\circ}$ C to  $+85^{\circ}$ C. Typical specifications at  $+25^{\circ}$ C. All specifications at AVDD = DVDD = VREFP = +5V,  $V_{CM} = 2.5$ V and VREFN = GND, unless otherwise noted.

|                                                                 |                                   |                                                                                                  |             | ADS1231                      |             |             |

|-----------------------------------------------------------------|-----------------------------------|--------------------------------------------------------------------------------------------------|-------------|------------------------------|-------------|-------------|

| PARA                                                            | METER                             | CONDITIONS                                                                                       | MIN         | TYP                          | MAX         | UNIT        |

| ANALOG INPUTS                                                   |                                   |                                                                                                  | 1           |                              |             |             |

|                                                                 |                                   |                                                                                                  |             | ±0.5V <sub>REF</sub> / 128   |             | V           |

| Full-scale input voltage (AINP – AINN)  Common-mode input range |                                   | V <sub>REF</sub> = AVDD = 5V                                                                     |             | ±19.5                        |             | mV          |

|                                                                 |                                   | $V_{REF} = AVDD = 3V$                                                                            |             | ±11.7                        |             | mV          |

| Common-mode inp                                                 | ut range                          |                                                                                                  | GND + 1.5   |                              | AVDD – 1.5  | V           |

| Differential input current                                      |                                   |                                                                                                  |             | ±2                           |             | nA          |

| LOW-SIDE POWE                                                   | R SWITCH                          |                                                                                                  |             |                              |             |             |

|                                                                 |                                   | $AVDD = 5V$ , $I_{SW} = 30mA$                                                                    |             | 3.5                          | 5           | Ω           |

| On-resistance (R <sub>ON</sub>                                  | 1)                                | AVDD = 3V, I <sub>SW</sub> = 30mA                                                                |             | 4                            | 7           | Ω           |

| Current through sw                                              | itch                              | - 3.1                                                                                            |             |                              | 30          | mA          |

| SYSTEM PERFOR                                                   |                                   |                                                                                                  |             |                              |             |             |

| Resolution                                                      |                                   | No missing codes                                                                                 | 24          |                              |             | Bits        |

|                                                                 |                                   | Internal oscillator, SPEED = high                                                                |             | 80                           |             | SPS         |

|                                                                 |                                   | Internal oscillator, SPEED = low                                                                 |             | 10                           |             | SPS         |

| Data rate                                                       |                                   | External clock, SPEED = high                                                                     |             | f <sub>CLKIN</sub> / 61,440  |             | SPS         |

|                                                                 |                                   | External clock, SPEED = low                                                                      |             | f <sub>CLKIN</sub> / 491,520 |             | SPS         |

| Digital filter settling                                         | time                              | Full settling                                                                                    |             | 4                            |             | Conversions |

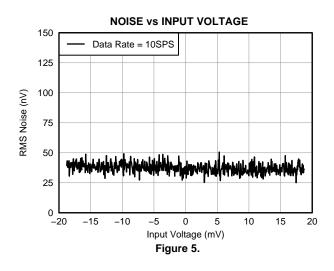

| g                                                               |                                   | f <sub>DATA</sub> = 10SPS, AVDD = V <sub>REF</sub> = 5V                                          |             | 35                           |             | nV, rms     |

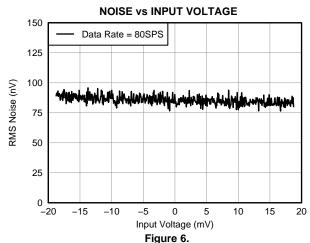

| Noise                                                           |                                   | $f_{DATA} = 80SPS, AVDD = V_{REF} = 5V$                                                          |             | 102                          |             | nV, rms     |

|                                                                 |                                   | f <sub>DATA</sub> = 10SPS, AVDD = V <sub>REF</sub> = 5V                                          |             | 232                          |             | nV, P-P     |

|                                                                 |                                   | $f_{DATA} = 80SPS, AVDD = V_{REF} = 5V$                                                          |             | 622                          |             | nV, P-P     |

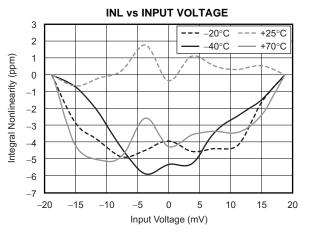

| Integral nonlinearity (INL)                                     |                                   | Differential input, end-point fit                                                                |             | ±8                           |             | ppm         |

| Input offset error                                              | ()                                |                                                                                                  |             | 10                           |             | μV          |

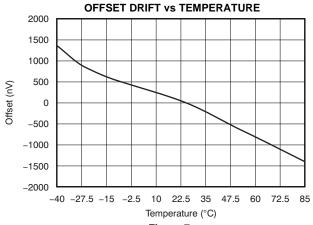

| Input offset drift                                              |                                   |                                                                                                  |             | ±20                          |             | nV/°C       |

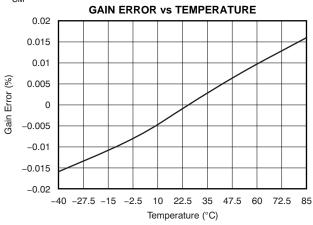

| Gain error                                                      |                                   |                                                                                                  |             | 1                            |             | %           |

| Gain drift                                                      |                                   |                                                                                                  |             | ±2                           |             | ppm/°C      |

|                                                                 | .: (1)                            | f <sub>IN</sub> = 50Hz or 60Hz ±1Hz, f <sub>DATA</sub> = 10SPS,<br>internal oscillator           | 80          | 100                          |             | dB          |

| Normal-mode rejec                                               | tion(1)                           | f <sub>IN</sub> = 50Hz or 60Hz ±1Hz, f <sub>DATA</sub> = 10SPS,<br>external clock <sup>(2)</sup> | 90          | 110                          |             | dB          |

| Common-mode reje                                                | ection                            | At dc                                                                                            |             | 110                          |             | dB          |

| Power-supply reject                                             | tion                              | At dc                                                                                            | 90          | 100                          |             | dB          |

| VOLTAGE REFER                                                   | ENCE INPUT                        |                                                                                                  |             |                              |             |             |

| Voltage reference in                                            | nput (V <sub>REF</sub> )          | V <sub>REF</sub> = VREFP - VREFN                                                                 | 1.5         | AVDD                         | AVDD + 0.1  | V           |

| Negative reference                                              | input (VREFN)                     |                                                                                                  | GND - 0.1   |                              | VREFP – 1.5 | V           |

| Positive reference i                                            | nput (VREFP)                      |                                                                                                  | VREFN + 1.5 |                              | AVDD + 0.1  | V           |

| Voltage reference input current                                 |                                   |                                                                                                  |             | 10                           |             | nA          |

| DIGITAL INPUT/O                                                 | UTPUT (DVDD = 3V to               | 5.3V)                                                                                            |             |                              |             |             |

|                                                                 | V <sub>IH</sub>                   |                                                                                                  | 0.8 DVDD    |                              | DVDD + 0.1  | V           |

|                                                                 | V <sub>IL</sub>                   |                                                                                                  | GND         |                              | 0.2 DVDD    | V           |

| Logic levels                                                    | V <sub>OH</sub>                   | I <sub>OH</sub> = 500μA                                                                          | DVDD - 0.4  |                              |             | V           |

|                                                                 | V <sub>OL</sub>                   | I <sub>OL</sub> = 500µA                                                                          |             |                              | 0.2 DVDD    | V           |

| Input leakage                                                   | 1                                 | 0 < V <sub>DIGITAL INPUT</sub> < DVDD                                                            |             |                              | ±10         | μA          |

| External clock input                                            | t frequency (f <sub>CLKIN</sub> ) | 2.0                                                                                              | 1           | 4.9152                       | 6           | MHz         |

| Serial clock input fr                                           |                                   |                                                                                                  |             |                              | 5           | MHz         |

<sup>(1)</sup> Specification is assured by the combination of design and final test.

<sup>(2)</sup>  $f_{CLKIN} = 4.9152MHz$ .

### **ELECTRICAL CHARACTERISTICS (continued)**

Minimum/maximum limit specifications apply from  $-40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ . Typical specifications at  $+25^{\circ}\text{C}$ . All specifications at AVDD = DVDD = VREFP = +5V,  $\text{V}_{\text{CM}}$  = 2.5V and VREFN = GND, unless otherwise noted.

|                                   |                                      | ADS1231 |     |     |          |  |

|-----------------------------------|--------------------------------------|---------|-----|-----|----------|--|

| PARAMETER                         | CONDITIONS                           | MIN     | TYP | MAX | UNIT     |  |

| POWER SUPPLY                      |                                      |         |     |     |          |  |

| Power-supply voltage (AVDD, DVDD) |                                      | 3       |     | 5.3 | V        |  |

|                                   | Normal mode, AVDD = 3V               |         | 900 |     | μA       |  |

| Analog gunnhi gurrant             | Normal mode, AVDD = 5V               |         | 900 |     | μA       |  |

| Analog supply current             | Standby mode                         |         | 0.1 |     | μA       |  |

|                                   | Power-down                           |         | 0.1 |     | μA       |  |

|                                   | Normal mode, DVDD = 3V               |         | 60  |     | μA       |  |

|                                   | Normal mode, DVDD = 5V               |         | 95  |     | μA       |  |

| Digital supply current            | Standby mode, SCLK = high, DVDD = 3V |         | 45  |     | μA       |  |

|                                   | Standby mode, SCLK = high, DVDD = 5V |         | 65  |     | μA       |  |

|                                   | Power-down                           |         | 0.2 |     | μA       |  |

| Down discipation total            | Normal mode, AVDD = DVDD = 3V        |         | 2.9 |     | mW       |  |

| Power dissipation, total          | Normal mode, AVDD = DVDD = 5V        |         | 5   |     | mW       |  |

| TEMPERATURE                       |                                      |         |     |     | <u> </u> |  |

| Operating temperature range       |                                      | -40     |     | +85 | °C       |  |

| Specified temperature range       |                                      | -40     |     | +85 | °C       |  |

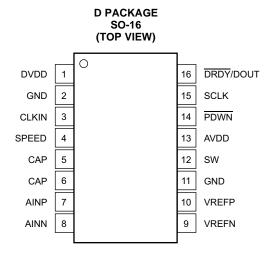

### **PIN CONFIGURATION**

### **PIN DESCRIPTIONS**

| NAME      | TERMINAL | ANALOG/DIGITAL INPUT/OUTPUT | DESCRIPTION                                                                                                                                 |

|-----------|----------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| DVDD      | 1        | Digital                     | Digital power supply                                                                                                                        |

| GND       | 2        | Supply                      | Ground for digital and analog supplies                                                                                                      |

| CLKIN     | 3        | Digital input               | External clock input: typically 4.9152MHz. Tie low to activate internal oscillator.                                                         |

|           |          |                             | Data rate select:                                                                                                                           |

| 00550     |          | D: :: 1:                    | SPEED DATA RATE                                                                                                                             |

| SPEED     | 4        | Digital input               | 0 10SPS                                                                                                                                     |

|           |          |                             | 1 80SPS                                                                                                                                     |

| CAP       | 5        | Analog                      | Gain amplifier bypass capacitor connection                                                                                                  |

| CAP       | 6        | Analog                      | Gain amplifier bypass capacitor connection                                                                                                  |

| AINP      | 7        | Analog input                | Positive analog input                                                                                                                       |

| AINN      | 8        | Analog input                | Negative analog input                                                                                                                       |

| VREFN     | 9        | Analog input                | Negative reference input                                                                                                                    |

| VREFP     | 10       | Analog input                | Positive reference input                                                                                                                    |

| GND       | 11       | Supply                      | Ground for digital and analog supplies                                                                                                      |

| SW        | 12       | Analog                      | Low-side power switch                                                                                                                       |

| AVDD      | 13       | Supply                      | Analog power supply                                                                                                                         |

| PDWN      | 14       | Digital input               | Power-down: holding this pin low powers down the entire converter and resets the ADC.                                                       |

| SCLK      | 15       | Digital input               | Serial clock: clock out data on the rising edge. Also used to initiate Standby mode. See the Standby Mode section for more details.         |

| DRDY/DOUT | 16       | Digital output              | Dual-purpose output: Data ready: indicates valid data by going low. Data output: outputs data, MSB first, on the first rising edge of SCLK. |

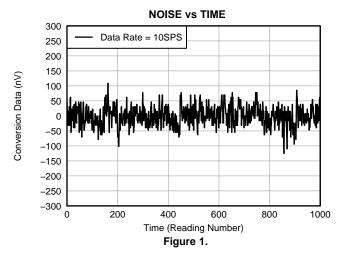

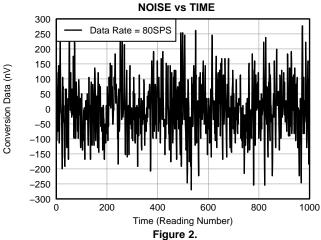

#### **NOISE PERFORMANCE**

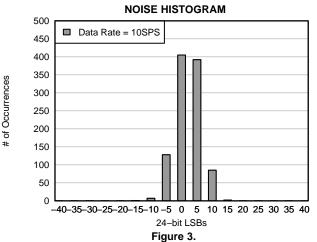

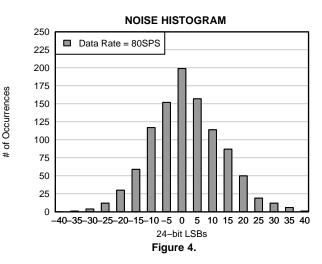

The ADS1231 offers outstanding noise performance. Table 1 summarizes the typical noise performance with inputs shorted externally for different data rates and voltage reference values.

The RMS and Peak-to-Peak noise are referred to the input. The effective number of bits (ENOB) is defined as: ENOB = In (FSR/RMS noise)/In(2)

The Noise-Free Bits are defined as:

Noise-Free Bits = In (FSR/Peak-to-Peak Noise)/In(2)

Where:

FSR (Full-Scale Range) = V<sub>REF</sub>/Gain.

**Table 1. Noise Performance**

| DATA RATE | AVDD and V <sub>REF</sub> (V) | RMS NOISE <sup>(1)</sup><br>(nV) | PEAK-TO-PEAK NOISE <sup>(1)</sup> (nV) | ENOB<br>(RMS) | NOISE-FREE BITS |

|-----------|-------------------------------|----------------------------------|----------------------------------------|---------------|-----------------|

| 10        | 5                             | 35.2                             | 231.9                                  | 20.1          | 17.4            |

| 10        | 3                             | 33.5                             | 199.2                                  | 19.4          | 16.8            |

| 80        | 5                             | 102.1                            | 622.1                                  | 18.5          | 15.9            |

| 80        | 3                             | 80.3                             | 549.6                                  | 18.2          | 15.4            |

<sup>(1)</sup> Noise specifications are based on direct measurement of 1024 consecutive samples.

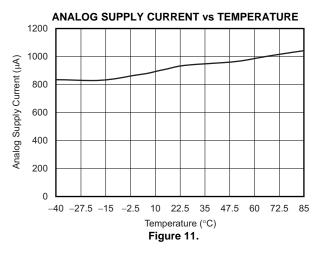

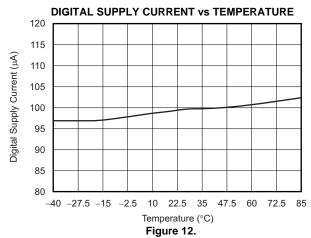

#### TYPICAL CHARACTERISTICS

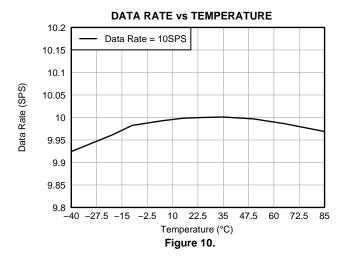

At  $T_A = +25$ °C, AVDD = DVDD = REFP = 5V, REFN = GND, and  $V_{CM} = 2.5$ V unless otherwise noted.

### **TYPICAL CHARACTERISTICS (continued)**

At  $T_A = +25$ °C, AVDD = DVDD = REFP = 5V, REFN = GND, and  $V_{CM} = 2.5$ V unless otherwise noted.

Figure 7.

Figure 8.

Figure 9.

#### OVERVIEW

The ADS1231 is a precision, 24-bit ADC that includes a low-noise PGA, internal oscillator, third-order delta-sigma ( $\Delta\Sigma$ ) modulator, and fourth-order digital filter. The ADS1231 provides a complete front-end solution for bridge sensor applications such as weigh scales, strain gauges, and pressure sensors.

Data can be output at 10SPS for excellent 50Hz and 60Hz rejection, or at 80SPS when higher speeds are needed. The ADS1231 is easy to configure, and all digital control is accomplished through dedicated pins; there are no registers to program. A simple two-wire serial interface retrieves the data.

### **ANALOG INPUTS (AINP, AINN)**

The input signal to be measured is applied to the input pins AINP and AINN. The ADS1231 accepts differential input signals, but can also measure unipolar signals.

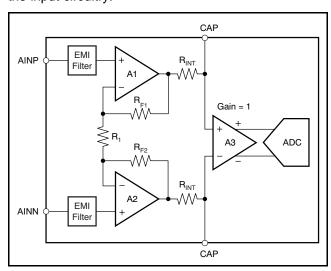

#### **LOW-NOISE AMPLIFIER**

The ADS1231 features a low-drift, low-noise amplifier that provides a complete front-end solution for bridge sensors. A simplified diagram of the amplifier is shown in Figure 13. It consists of two chopperstabilized amplifiers (A1 and A2) and three accurately matched resistors (R<sub>1</sub>, R<sub>F1</sub>, and R<sub>F2</sub>) that construct a differential front-end stage with a gain of 128, followed by gain stage A3 (Gain = 1). The inputs are equipped with an EMI filter, as shown in Figure 13. The cutoff frequency of the EMI filter is 20MHz. By using AVDD as the reference input, the bipolar input ranges from -19.5mV to +19.5mV. The inputs of the ADS1231 are protected with internal diodes connected to the power-supply rails. These diodes clamp the applied signal to prevent it from damaging the input circuitry.

Figure 13. Simplified Diagram of the Amplifier

#### **External Capacitor**

An external capacitor (C<sub>EXT</sub>) across the two ADS1231 CAP pins combines with the internal resistor R<sub>INT</sub> (onchip) to create a low-pass filter. The recommended value for  $C_{EXT}$  is  $0.1\mu F$  which provides a corner frequency of 720Hz. This low-pass filter serves two purposes. First, the input signal is bandlimited to prevent aliasing by the ADC and to filter out the highfrequency noise. Second, it attenuates the chopping residue from the amplifier to improve temperature drift performance. NPO or C0G capacitors recommended. For optimal performance, place the external capacitor very close to the CAP pins.

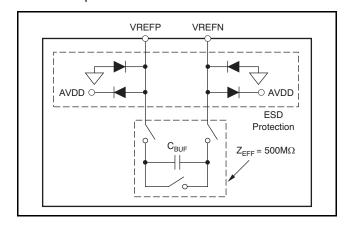

# VOLTAGE REFERENCE INPUTS (VREFP, VREFN)

The voltage reference used by the modulator is generated from the voltage difference between VREFP and VREFN:  $V_{REF} = VREFP - VREFN$ . The reference inputs use a structure similar to that of the analog inputs. In order to increase the reference input impedance, switching buffer circuitry is used to reduce the input equivalent capacitance. The reference drift and noise impact ADC performance. In order to achieve best results, pay close attention to the reference noise and drift specifications. A simplified diagram of the circuitry on the reference inputs is shown in Figure 14. The switches and capacitors can be modeled approximately using an effective impedance of  $Z_{EFF} = 500 M\Omega$ .

Figure 14. Simplified Reference Input Circuitry

ESD diodes protect the reference inputs. To prevent these diodes from turning on, make sure the voltages on the reference pins do not go below GND by more than 100mV, and likewise, do not exceed AVDD by 100mV:

GND - 100mV < (VREFP or VREFN) < AVDD + 100mV

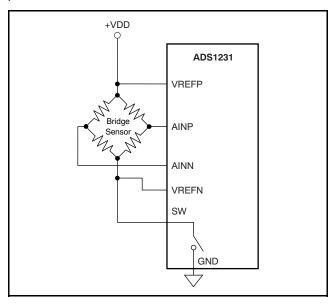

### **LOW-SIDE POWER SWITCH (SW)**

The ADS1231 incorporates an internal switch for use with an external bridge sensor, as shown in Figure 15. The switch can be used in a return path for the bridge power. By opening the switch, power dissipation in the bridge is eliminated.

The switch is controlled by the ADS1231 conversion status. During normal conversions, the switch is closed (the SW pin is connected to GND). During standby or power-down modes, the switch is opened (the SW pin is high impedance). When using the switch, it is recommended that the negative reference input (VREFN) be connected directly to the bridge ground terminal, as shown in Figure 15 for best performance.

Figure 15. Low-Side Power Switch

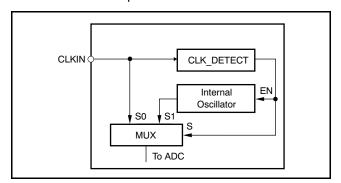

#### **CLOCK SOURCE**

The ADS1231 can use the internal oscillator or an external clock source to accomodate a wide variety of applications. Figure 16 shows the equivalent circuitry of the clock module. The CLK\_DETECT block determines whether an external clock signal is applied to the CLKIN pin so that the internal oscillator is bypassed or activated. When the CLKIN pin frequency is above ~200kHz, the CLK\_DETECT circuit shuts down the internal oscillator and passes the external clock signal to the ADC. When the CLKIN pin frequency is below ~200kHz, the CLK\_DETECT block activates the internal oscillator. When the internal oscillator is chosen, make sure to connect the CLKIN pin to GND.

Figure 16. Equivalent Circuitry of the Clock Source

The allowable frequency range for the external clock signal  $f_{\text{CLKIN}}$  is specified in the Electrical Characteristics table.

www.ti.com.cn

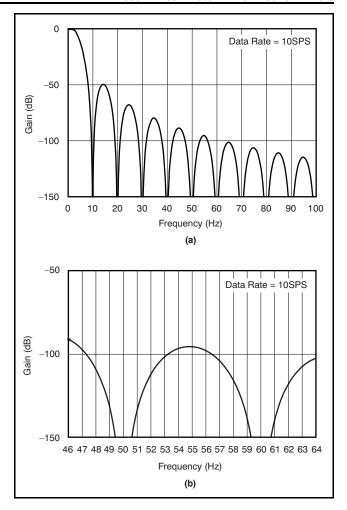

#### FREQUENCY RESPONSE

The ADS1231 uses a  $\rm sinc^4$  digital filter with the frequency response shown in Figure 17 for  $\rm f_{CLKIN}$  = 4.9152MHz. The frequency response repeats at multiples of the modulator sampling frequency of 76.8kHz. The overall response is that of a low-pass filter with a -3dB cutoff frequency of 3.32Hz with the SPEED pin tied low (10SPS data rate) and 11.64Hz with the SPEED pin tied high (80SPS data rate).

To help see the response at lower frequencies, Figure 17(a) illustrates the nominal response out to 100Hz, when the data rate = 10SPS. Notice that signals at multiples of 10Hz are rejected, and therefore simultaneous rejection of 50Hz and 60Hz is achieved.

The benefit of using a sinc<sup>4</sup> filter is that every frequency notch has four zeros on the same location, thus providing excellent normal-mode rejection of line-cycle interference.

Figure 17(b) zooms in on the 50Hz and 60Hz notches with the SPEED pin tied low (10SPS data rate).

The ADS1231 data rate and frequency response scale directly with clock frequency. For example, if  $f_{\text{CLKIN}}$  increases from 4.9152MHz to 5.5296MHz when the SPEED pin is tied high, the data rate increases from 80SPS to 90SPS, while the notch also increases from 80Hz to 90Hz. Note that these changes are only possible when an external clock source is applied.

Figure 17. Nominal Frequency Response Out To 100Hz

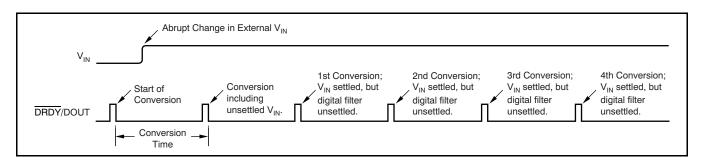

### **SETTLING TIME**

Fast changes in the input signal require time to settle. For example, an external multiplexer in front of the ADS1231 can generate abrupt changes in input voltage by simply switching the multiplexer input channels. These sorts of changes in the input require four data conversion cycles to settle. When continuously converting, five readings may be necessary in order to settle the data. If the change in input occurs in the middle of the first conversion, four more full conversions of the fully-settled input are required to obtain fully-settled data. Discard the first four readings because they contain only partially-settled data. Figure 18 illustrates the settling time for the ADS1231.

#### **DATA RATE**

The ADS1231 data rate is set by the SPEED pin, as shown in Table 2. When SPEED is low, the data rate is nominally 10SPS. This data rate provides the lowest noise, and also has excellent rejection of both 50Hz and 60Hz line-cycle interference. For applications requiring fast data rates, setting SPEED high selects a data rate of nominally 80SPS.

**Table 2. Data Rate Settings**

|           | DATA RATE           |                              |  |  |

|-----------|---------------------|------------------------------|--|--|

| SPEED PIN | Internal Oscillator | External Clock               |  |  |

| 0         | 10SPS               | f <sub>CLKIN</sub> / 491,520 |  |  |

| 1         | 80SPS               | f <sub>CLKIN</sub> / 61,440  |  |  |

#### **DATA FORMAT**

The ADS1231 outputs 24 bits of data in binary twos complement format. The least significant bit (LSB) has a weight of  $(0.5V_{REF}/128)(2^{23}-1)$ . The positive full-scale input produces an output code of 7FFFFh and the negative full-scale input produces an output code of 800000h. The output clips at these codes for signals exceeding full-scale. Table 3 summarizes the ideal output codes for different input signals.

Table 3. Ideal Output Code vs Input Signal

| INPUT SIGNAL V <sub>IN</sub><br>(AINP – AINN)     | IDEAL OUTPUT |

|---------------------------------------------------|--------------|

| ≥ +0.5V <sub>REF</sub> /128                       | 7FFFFh       |

| (+0.5V <sub>REF</sub> /128)/(2 <sup>23</sup> - 1) | 000001h      |

| 0                                                 | 000000h      |

| (-0.5V <sub>REF</sub> /128)/(2 <sup>23</sup> - 1) | FFFFFh       |

| ≤ -0.5V <sub>REF</sub> /128                       | 800000h      |

Excludes effects of noise, INL, offset, and gain errors.

Figure 18. Settling Time in Continuous Conversion Mode

### DATA READY/DATA OUTPUT (DRDY/DOUT)

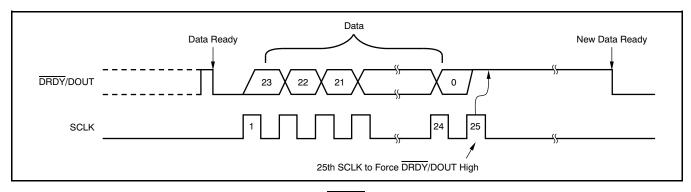

This digital output pin serves two purposes. First, it indicates when new data are ready by going low. Afterwards, on the first rising edge of SCLK, the DRDY/DOUT pin changes function and begins outputting the conversion data, most significant bit (MSB) first. Data are shifted out on each subsequent SCLK rising edge. After all 24 bits have been retrieved, the pin can be forced high with an additional SCLK. It then stays high until new data are ready. This configuration is useful when polling on the status of DRDY/DOUT to determine when to begin data retrieval.

### SERIAL CLOCK INPUT (SCLK)

This digital input shifts serial data out with each rising edge. This input has built-in hysteresis, but care should still be taken to ensure a clean signal. Glitches or slow-rising signals can cause unwanted additional shifting. For this reason, it is best to make sure the rise and fall times of SCLK are both less than 50ns.

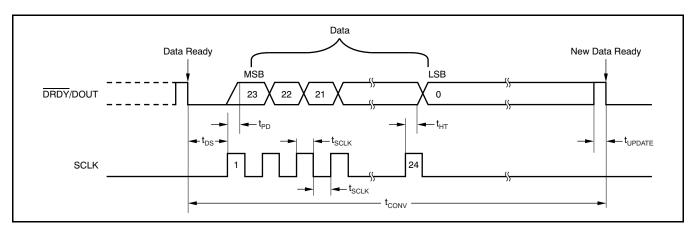

#### DATA RETRIEVAL

The ADS1231 continuously converts the analog input signal. To retrieve data, wait until DRDY/DOUT goes low, as shown in Figure 19. After DRDY/DOUT goes low, begin shifting out the data by applying SCLKs. Data are shifted out MSB first. It is not required to shift out all 24 bits of data, but the data must be retrieved before new data are updated (within t<sub>CONV</sub>) or else the data will be overwritten. Avoid data retrieval during the update period (tuppate). If only 24 SCLKs have been applied, DRDY/DOUT remains at the state of the last bit shifted out until it is taken high (see t<sub>UPDATE</sub>), indicating that new data are being updated. To avoid having DRDY/DOUT remain in the state of the last bit, the 25th SCLK can be applied to force DRDY/DOUT high, as shown in Figure 20. This technique is useful when a host controlling the device is polling DRDY/DOUT to determine when data are ready.

Figure 19. 24-Bit Data Retrieval Timing

| SYMBOL                         | DESCRIPTION                                               |                                         | MIN | TYP  | MAX | UNITS |

|--------------------------------|-----------------------------------------------------------|-----------------------------------------|-----|------|-----|-------|

| t <sub>DS</sub>                | DRDY/DOUT low to first SCLK rising 6                      | DRDY/DOUT low to first SCLK rising edge |     |      |     | ns    |

| t <sub>SCLK</sub>              | SCLK positive or negative pulse width                     |                                         | 100 |      |     | ns    |

| t <sub>PD</sub> <sup>(1)</sup> | SCLK rising edge to new data bit valid: propagation delay |                                         |     |      | 50  | ns    |

| t <sub>HT</sub> <sup>(1)</sup> | SCLK rising edge to old data bit valid: hold time         |                                         | 20  |      |     | ns    |

| t <sub>UPDATE</sub>            | Data updating: no readback allowed                        |                                         |     | 90   |     | μs    |

|                                | Conversion time (4/data rata)                             | SPEED = 1                               |     | 12.5 |     | ms    |

| t <sub>CONV</sub>              | Conversion time (1/data rate)  SPEED = 0                  |                                         |     | 100  |     | ms    |

<sup>(1)</sup> Minimum required from simulation.

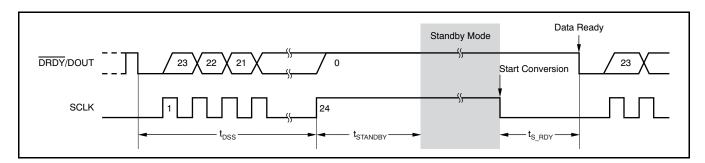

### **STANDBY MODE**

Standby mode dramatically reduces power consumption by shutting down most of the circuitry. To enter Standby mode, simply hold SCLK high after DRDY/DOUT goes low; see Figure 21. Standby mode can be initiated at any time during readback; it is not necessary to retrieve all 24 bits of data beforehand.

When t<sub>STANDBY</sub> has passe<u>d with</u> SCLK held high, Standby mode activates. DRDY/DOUT stays high when Standby mode begins. SCLK must remain high to stay in Standby mode. To exit Standby mode (wakeup), set SCLK low. The first data after exiting Standby mode are valid.

Figure 20. Data Retrieval with DRDY/DOUT Forced High Afterwards

Figure 21. Standby Mode Timing (Can be used for single conversions)

| SYMBOL                          | DESCRIPTION                       |           | MIN  | TYP   | MAX   | UNITS |

|---------------------------------|-----------------------------------|-----------|------|-------|-------|-------|

| t <sub>DSS</sub> <sup>(1)</sup> | SCLK high after DRDY/DOUT         | SPEED = 1 |      |       | 12.44 | ms    |

|                                 | goes low to activate Standby mode | SPEED = 0 |      |       | 99.94 | ms    |

| t <sub>STANDBY</sub>            | Standby mode activation time      | SPEED = 1 | 12.5 |       |       | ms    |

|                                 |                                   | SPEED = 0 | 100  |       |       | ms    |

| t <sub>S_RDY</sub> (1)          | Data ready after exiting Standby  | SPEED = 1 |      | 52.6  |       | ms    |

|                                 |                                   | SPEED = 0 |      | 401.8 |       | ms    |

<sup>(1)</sup> Based on an ideal internal oscillator.

www.ti.com.cn

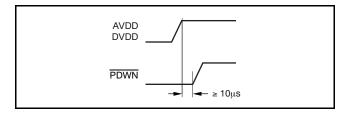

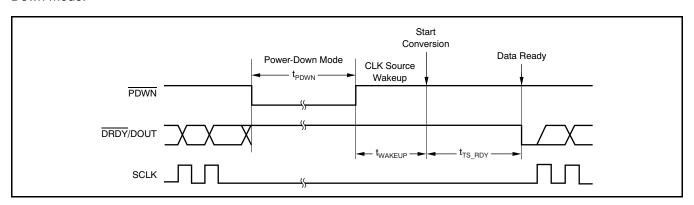

#### **POWER-DOWN MODE**

Power-Down mode shuts down the entire ADC circuitry and reduces the total power consumption close to zero. To enter Power-Down mode, simply hold the PDWN pin low. Power-Down mode also resets the entire circuitry. Power-Down mode can be initiated at any time during readback; it is not necessary to retrieve all 24 bits of data beforehand. Figure 23 shows the wake-up timing from Power-Down mode.

Figure 22. Power-Up Timing Sequence

Figure 23. Wake-Up Timing from Power-Down Mode

| SYMBOL                           | DESCRIPTION                        | MIN | TYP  | UNITS |

|----------------------------------|------------------------------------|-----|------|-------|

| t <sub>WAKEUP</sub> (1)(2)       | Wake-up time after Power-Down mode |     | 7.95 | рs    |

| t <sub>PDWN</sub> <sup>(1)</sup> | PDWN pulse width                   | 26  |      | μs    |

- (1) Based on an ideal internal oscillator.

- (2) Typical required from simulation.

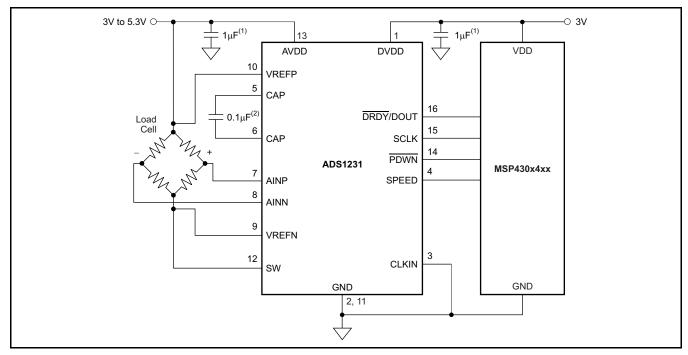

### **APPLICATION EXAMPLE**

### Weigh Scale System

Figure 24 shows a typical ADS1231 application as part of a weigh scale system.

- (1) Place a  $0.1\mu F$  or higher capacitor as close as possible on both AVDD and DVDD.

- (2) Place capacitor very close to the ADS1231 CAP pins for optimal performance.

Figure 24. Weigh Scale Example

### **REVISION HISTORY**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| CI | hanges from Revision C (December 2010) to Revision D                                            | Page |

|----|-------------------------------------------------------------------------------------------------|------|

| •  | Changed "oscillator" to "clock in data rate parameter of electrical characteristics             | 3    |

| •  | Changed all "f <sub>CLK</sub> " to "f <sub>CLKIN</sub> " throughout data sheet                  | 3    |

| •  | Deleted extra space in data rate parameter typical value (typo)                                 | 3    |

| •  | Changed "oscillator" to "clock in data rate parameter of electrical characteristics             | 3    |

| •  | Deleted extra space in data rate parameter typical value (typo)                                 | 3    |

| •  | Changed location of noise parameter                                                             | 3    |

| •  | Changed "oscillator" to "clock in normal-mode rejection parameter of electrical characteristics | 3    |

| •  | Changed "AGND" to "GND" in negative reference input parameter min value                         | 3    |

| •  | Added new external clock input frequency paramter                                               | 3    |

| •  | Changed "oscillator" to "f <sub>CLKIN</sub> " in note 2 of electrical characteristics           | 3    |

| •  | Changed pin 12 name from PSW to SW in pinout drawing                                            | 5    |

| •  | Changed pin 12 name from PSW to SW in Pin Descriptions table                                    | 5    |

| •  | Changed title of Figure 5                                                                       | 7    |

| •  | Changed title of Figure 6                                                                       | 7    |

| •  | Changed plot title and X-axis label of Figure 9                                                 | 8    |

| •  | Changed plot title and Y-axis label of Figure 11                                                | 8    |

| •  | Changed plot title and Y-axis label of Figure 12                                                | 8    |

| •  | Changed Clock Source section                                                                    | 10   |

| •  | Added text to first sentence of Frequency Response section                                      | 11   |

| •  | Changed third paragraph of Frequency Response secton                                            | 11   |

| •  | Added new text to end of Frequency Response section                                             | 11   |

| •  | Changed Table 2                                                                                 | 12   |

| •  | Changed pin numbers in Figure 24 to match the device pinout and added missing CLKIN pin         | 16   |

17

www.ti.com 2-May-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins | Package qty   Carrier | RoHS | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|--------|---------------|----------------|-----------------------|------|-------------------------------|----------------------------|--------------|------------------|

|                       |        |               |                |                       |      | (4)                           | (5)                        |              |                  |

| ADS1231ID             | Active | Production    | SOIC (D)   16  | 40   TUBE             | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 85    | ADS1231          |

| ADS1231IDR            | Active | Production    | SOIC (D)   16  | 2500   LARGE T&R      | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 85    | ADS1231          |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

## **PACKAGE MATERIALS INFORMATION**

www.ti.com 25-Sep-2024

### TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

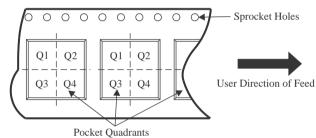

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device     | U    | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|------------|------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| ADS1231IDR | SOIC | D                  | 16 | 2500 | 330.0                    | 16.4                     | 6.5        | 10.3       | 2.1        | 8.0        | 16.0      | Q1               |

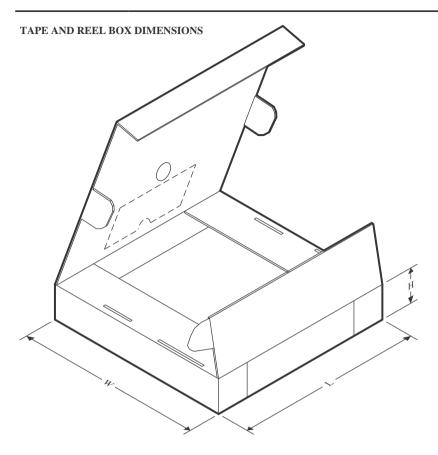

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 25-Sep-2024

### \*All dimensions are nominal

| Device     | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |  |

|------------|--------------|-----------------|------|------|-------------|------------|-------------|--|

| ADS1231IDR | SOIC         | D               | 16   | 2500 | 353.0       | 353.0      | 32.0        |  |

# **PACKAGE MATERIALS INFORMATION**

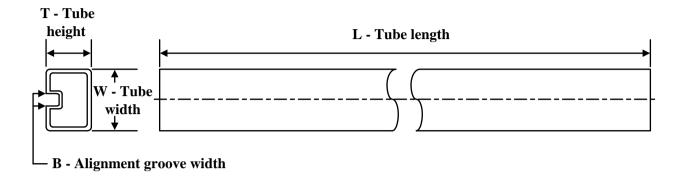

www.ti.com 25-Sep-2024

### **TUBE**

### \*All dimensions are nominal

| Device    | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (µm) | B (mm) |  |

|-----------|--------------|--------------|------|-----|--------|--------|--------|--------|--|

| ADS1231ID | D            | SOIC         | 16   | 40  | 507    | 8      | 3940   | 4.32   |  |

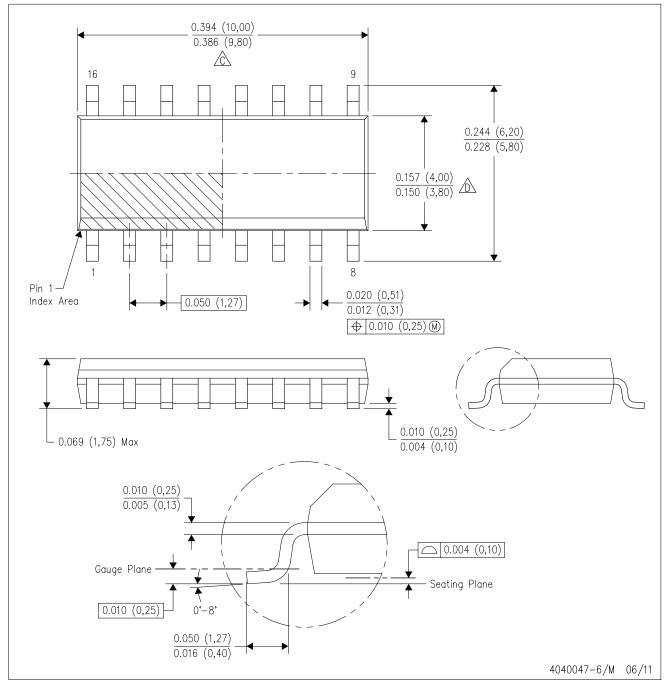

# D (R-PDS0-G16)

### PLASTIC SMALL OUTLINE

NOTES:

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.006 (0,15) each side.

- Body width does not include interlead flash. Interlead flash shall not exceed 0.017 (0,43) each side.

- E. Reference JEDEC MS-012 variation AC.

### 重要通知和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。 严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 版权所有 © 2025,德州仪器 (TI) 公司