ZHCSII6C - JULY 2018 - REVISED JANUARY 2023

#### OPA8558GHz 增益带宽积、 7V/V 稳定增益、 双极输入放大器

### 1 特性

高增益带宽积:8GHz

Instruments

解补偿,增益 ≥ 7V/V (稳定) 低输入电压噪声: 0.98nV/√Hz

• 压摆率: 2750V/µs

• 低输入电容:

**TEXAS**

- 共模: 0.6pF - 差分: 0.2pF 宽输入共模范围:

- 与正电源相差 0.4V

与负电源相差 1.1V

3V<sub>PP</sub> 总输出摆幅

• 电源电压范围: 3.3V 至 5.25V

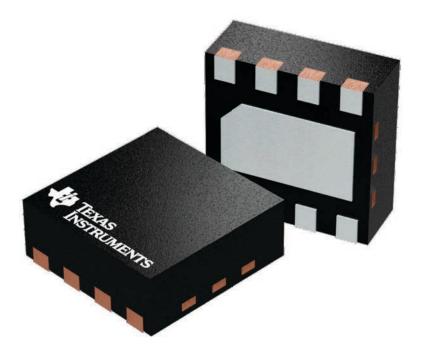

• 静态电流:17.8mA 封装:8引脚WSON - 裸片 (预发布)

• 温度范围: -40°C 至 +125°C

### 2 应用

光时域反射计 (OTDR)

3D 扫描仪

激光测距

固态扫描激光雷达

光学 ToF 位置传感器

无人机视觉

工业机器人激光雷达

扫地机器人激光雷达

硅光电倍增器 (SiPM) 缓冲放大器

光电倍增管后置放大器

高速飞行时间接收器

### 3 说明

OPA855 是一款具有双极输入的宽带低噪声运算放大 器,适用于宽带跨阻和电压放大器应用。将该器件配置 为跨阻放大器 (TIA) 时,8GHz 增益带宽积 (GBWP) 能 够以高达几十千欧的跨阻增益实现高闭环带宽。

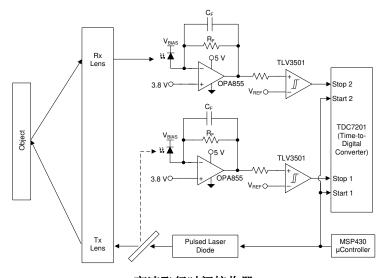

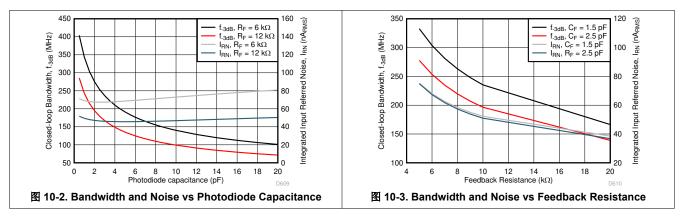

下图展示了将 OPA855 配置为 TIA 时,该放大器的带 宽和噪声性能与光电二极管电容的函数关系。计算总噪 声时的带宽范围为从直流到左轴上计算得出的频率 (f)。OPA855 封装具有一个反馈引脚 (FB),可简化输 入和输出之间的反馈网络连接。

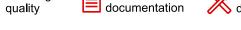

OPA855 经过优化,可在光学飞行时间 (ToF) 系统中运 行,在该系统中,OPA855 与时数转换器(如 TDC7201)配合使用。可在具有差分输出放大器(如 THS4541 或 LMH5401)的高分辨率激光雷达系统中 使用 OPA855 来驱动高速模数转换器 (ADC)。

#### 封装信息

| 器件型号 <sup>(1)</sup> | 封装            | 封装尺寸(标称值)         |

|---------------------|---------------|-------------------|

| OPA855              | WSON (DSG, 8) | 2.00 mm × 2.00 mm |

### 器件信息(3)

| 器件型号 <sup>(1)</sup> | 封装                | 芯片尺寸 ( 标称值 )        |

|---------------------|-------------------|---------------------|

| OPA855              | 裸片 <sup>(2)</sup> | 0.751 mm × 0.705 mm |

- (1) 如需了解所有可用封装,请参阅数据表末尾的封装选项附录。

- 预发布封装。 (2)

- 请参阅器件比较表。 (3)

光电二极管电容与带宽和噪声间的关系

### **Table of Contents**

| 1 特性                                 | 1  | 9.4 Device Functional Modes                         | 20                 |

|--------------------------------------|----|-----------------------------------------------------|--------------------|

| 2 应用                                 |    | 10 Application, Implementation, and Layout          |                    |

| 3 说明                                 |    | 10.1 Application Information                        | 21                 |

| 4 Revision History                   |    | 10.2 Typical Application                            | 21                 |

| 5 Device Comparison Table            |    | 10.3 Typical Application                            | 23                 |

| 6 Pin Configuration and Functions    |    | 10.4 Power Supply Recommendations                   | <mark>27</mark>    |

| 7 Specifications                     |    | 10.5 Layout                                         | 28                 |

| 7.1 Absolute Maximum Ratings         |    | 11 Device and Documentation Support                 | 30                 |

| 7.2 ESD Ratings                      |    | 11.1 Device Support                                 | 30                 |

| 7.3 Thermal Information              |    | 11.2 Documentation Support                          | 30                 |

| 7.4 Recommended Operating Conditions |    | 11.3 Receiving Notification of Documentation Update | es <mark>30</mark> |

| 7.5 Electrical Characteristics       |    | 11.4 支持资源                                           | 30                 |

| 7.6 Typical Characteristics          |    | 11.5 Trademarks                                     | 30                 |

| 8 Parameter Measurement Information  |    | 11.6 静电放电警告                                         | 30                 |

| 9 Detailed Description               | 16 | 11.7 术语表                                            | 30                 |

| 9.1 Overview                         |    | 12 Mechanical, Packaging, and Orderable             |                    |

| 9.2 Functional Block Diagram         |    | Information                                         | 30                 |

| 9.3 Feature Description              |    |                                                     |                    |

|                                      |    |                                                     |                    |

|                                      |    |                                                     |                    |

**4 Revision History** 注:以前版本的页码可能与当前版本的页码不同

| TT . WHANK LHADON A AND A THE ATTENDANCE LATE                                                   |      |

|-------------------------------------------------------------------------------------------------|------|

| Changes from Revision B (January 2022) to Revision C (January 2023)                             | Page |

| Added the Typical Application, Design Requirements, Detailed Design Procedure, and Applications |      |

| Changes from Revision A (October 2018) to Revision B (January 2022)                             | Page |

| • 更新了整个文档中的表格、图和交叉参考的编号格式                                                                       | 1    |

| • 在特性部分和器件信息表中添加了裸片预发布封装                                                                        | 1    |

| Added the bare die preview package to the Pin Configuration and Functions section               | 4    |

| Changes from Revision * (July 2018) to Revision A (October 2018)                                | Page |

| • 将"预告信息"更改为"量产数据(正在供货)"                                                                        | 1    |

# **5 Device Comparison Table**

| DEVICE INPUT TYPE |         | MINIMUM STABLE<br>GAIN | VOLTAGE NOISE (nV/<br>√ Hz) | INPUT<br>CAPACITANCE (pF) | GAIN BANDWIDTH<br>(GHz) |

|-------------------|---------|------------------------|-----------------------------|---------------------------|-------------------------|

| OPA855            | Bipolar | 7 V/V                  | 0.98                        | 0.8                       | 8                       |

| OPA856            | Bipolar | 1 V/V                  | 0.9                         | 1.1                       | 1.1                     |

| OPA858            | CMOS    | 7 V/V                  | 2.5                         | 0.8                       | 5.5                     |

| OPA859            | CMOS    | 1 V/V                  | 3.3                         | 0.8                       | 0.9                     |

| LMH6629           | Bipolar | 10 V/V                 | 0.69                        | 5.7                       | 4                       |

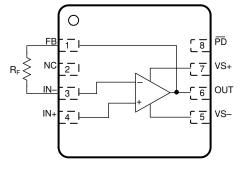

# **6 Pin Configuration and Functions**

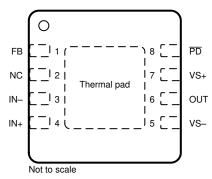

图 6-1. DSG Package, 8-Pin WSON With Exposed Thermal Pad (Top View)

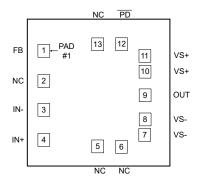

图 6-2. Bare Die Package (Preview)

表 6-1. Pin Functions

| PIN NAME NO. |   | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                           |  |  |

|--------------|---|---------------------|-----------------------------------------------------------------------------------------------------------------------|--|--|

|              |   | ITPE(''             |                                                                                                                       |  |  |

| FB           | 1 | I                   | Feedback connection to output of amplifier                                                                            |  |  |

| IN -         | 3 | I                   | Inverting input                                                                                                       |  |  |

| IN+ 4 I      |   | I                   | oninverting input                                                                                                     |  |  |

| NC 2 —       |   | _                   | Do not connect                                                                                                        |  |  |

| OUT 6 O      |   | 0                   | Amplifier output                                                                                                      |  |  |

| PD           | 8 | I                   | Power down connection. $\overline{PD}$ = logic low = power off mode; $\overline{PD}$ = logic high = normal operation. |  |  |

| VS - 5       |   | _                   | Negative voltage supply                                                                                               |  |  |

| VS+ 7        |   | _                   | Positive voltage supply                                                                                               |  |  |

| Thermal pad  |   | _                   | Connect the thermal pad to VS -                                                                                       |  |  |

表 6-2. Bond Pad Functions

| PAD TYPE(1) |              | TVDE(1)            | DESCRIPTION                                                                                                           |  |  |

|-------------|--------------|--------------------|-----------------------------------------------------------------------------------------------------------------------|--|--|

| NAME        | NO.          | ITPE               | DESCRIPTION                                                                                                           |  |  |

| FB          | 1            | I                  | Feedback connection to output of amplifier                                                                            |  |  |

| IN -        | 3            | I                  | Inverting input                                                                                                       |  |  |

| IN+         | 4            | I                  | Noninverting input                                                                                                    |  |  |

| NC          | 2,5,6,<br>13 | _                  | Do not connect                                                                                                        |  |  |

| OUT         | 9            | O Amplifier output |                                                                                                                       |  |  |

| PD          | 12           | I                  | Power down connection. $\overline{PD}$ = logic low = power off mode; $\overline{PD}$ = logic high = normal operation. |  |  |

| VS -        | VS - 7,8 —   |                    | Negative voltage supply                                                                                               |  |  |

| VS+ 10,11 — |              | _                  | Positive voltage supply                                                                                               |  |  |

| Backside    |              | _                  | Connect to VS -                                                                                                       |  |  |

(1) I = input, O = output, FB = feedback, NC = no connect

### 7 Specifications

### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                                      |                                                           | MIN                      | MAX              | UNIT |

|--------------------------------------|-----------------------------------------------------------|--------------------------|------------------|------|

| Vs                                   | Total supply voltage (V <sub>S+</sub> - V <sub>S-</sub> ) |                          | 5.5              | V    |

| V <sub>IN+</sub> , V <sub>IN</sub> - | Input voltage                                             | (V <sub>S</sub> -) - 0.5 | $(V_{S+}) + 0.5$ | V    |

| $V_{\text{ID}}$                      | Differential input voltage                                |                          | 1                | V    |

| VOUT                                 | Output voltage                                            | (V <sub>S</sub> -) - 0.5 | $(V_{S+}) + 0.5$ | V    |

| I <sub>IN</sub>                      | Continuous input current                                  |                          | ±10              | mA   |

| I <sub>OUT</sub>                     | Continuous output current <sup>(2)</sup>                  |                          | ±100             | mA   |

| $T_J$                                | Junction temperature                                      |                          | 150              | °C   |

| T <sub>A</sub>                       | Operating free-air temperature                            | - 40                     | 125              | °C   |

| T <sub>stg</sub>                     | Storage temperature                                       | - 65                     | 150              | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Rating may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Condition. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 7.2 ESD Ratings

|                    |                          |                                                                                     | VALUE | UNIT |

|--------------------|--------------------------|-------------------------------------------------------------------------------------|-------|------|

| V                  | Electrostatic discharge  | Human body model (HBM), per ANSI/ESDA/<br>JEDEC JS-001, all pins <sup>(1)</sup>     | ±1500 | V    |

| V <sub>(ESD)</sub> | Liectrostatic discriarge | Charged device model (CDM), per JEDEC specification JS-002, all pins <sup>(2)</sup> | ±1500 | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

#### 7.3 Thermal Information

|                        |                                              | OPA856 |      |

|------------------------|----------------------------------------------|--------|------|

|                        | DPA856   DSG (WSON)   UNIT                   |        |      |

|                        |                                              | 8 PINS |      |

| R <sub>0</sub> JA      | Junction-to-ambient thermal resistance       | 80.1   | °C/W |

| R <sub>θ JC(top)</sub> | Junction-to-case (top) thermal resistance    | 100    | °C/W |

| R <sub>0</sub> JB      | Junction-to-board thermal resistance         | 45     | °C/W |

| $\Psi_{JT}$            | Junction-to-top characterization parameter   | 6.8    | °C/W |

| Ψ ЈВ                   | Junction-to-board characterization parameter | 45.2   | °C/W |

| R <sub>θ JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 22.7   | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

### 7.4 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                |                                                           | MIN  | NOM | MAX  | UNIT |

|----------------|-----------------------------------------------------------|------|-----|------|------|

| Vs             | Total supply voltage (V <sub>S+</sub> - V <sub>S-</sub> ) | 3.3  | 5   | 5.25 | V    |

| T <sub>A</sub> | Operating free-air temperature                            | - 40 |     | 125  | °C   |

<sup>(2)</sup> Long-term continuous output current for electromigration limits.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 7.5 Electrical Characteristics

at  $V_{S+}$  = 5 V,  $V_{S-}$  = 0 V, G = 7 V/V,  $R_F$  = 453  $\Omega$ , input common-mode biased at midsupply,  $R_L$  = 200  $\Omega$ , output load is referenced to midsupply, and  $T_A$  = 25  $^{\circ}$ C (unless otherwise noted)

|                             | PARAMETER                        | TEST CONDITIONS                                                                    | MIN    | TYP    | MAX | UNIT     |

|-----------------------------|----------------------------------|------------------------------------------------------------------------------------|--------|--------|-----|----------|

| AC PERFO                    | DRMANCE                          | ,                                                                                  |        |        |     |          |

| SSBW                        | Small-signal bandwidth           | V <sub>OUT</sub> = 100 mV <sub>PP</sub>                                            |        | 2.5    |     | GHz      |

| LSBW                        | Large-signal bandwidth           | V <sub>OUT</sub> = 2 V <sub>PP</sub>                                               |        | 850    |     | MHz      |

| GBWP                        | Gain-bandwidth product           |                                                                                    |        | 8      |     | GHz      |

|                             | Bandwdith for 0.1-dB flatness    |                                                                                    |        | 200    |     | MHz      |

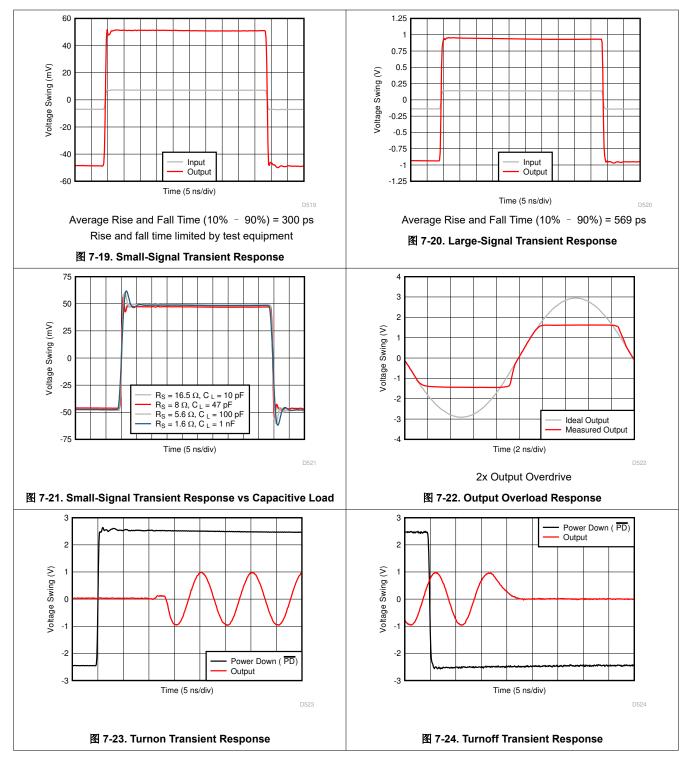

| SR                          | Slew rate (10%-90%)              | V <sub>OUT</sub> = 2-V step                                                        |        | 2750   |     | V/µs     |

| t <sub>r</sub>              | Rise time                        | V <sub>OUT</sub> = 100-mV step                                                     |        | 0.17   |     | ns       |

| t <sub>f</sub>              | Fall time                        | V <sub>OUT</sub> = 100-mV step                                                     |        | 0.17   |     | ns       |

|                             | Settling time to 0.1%            | V <sub>OUT</sub> = 2-V step                                                        |        | 2.3    |     | ns       |

|                             | Settling time to 0.001%          | V <sub>OUT</sub> = 2-V step                                                        |        | 2600   |     | ns       |

|                             | Overshoot or undershoot          | V <sub>OUT</sub> = 2-V step                                                        |        | 5%     |     |          |

|                             | Overdrive recovery               | 2x output overdrive                                                                |        | 3      |     | ns       |

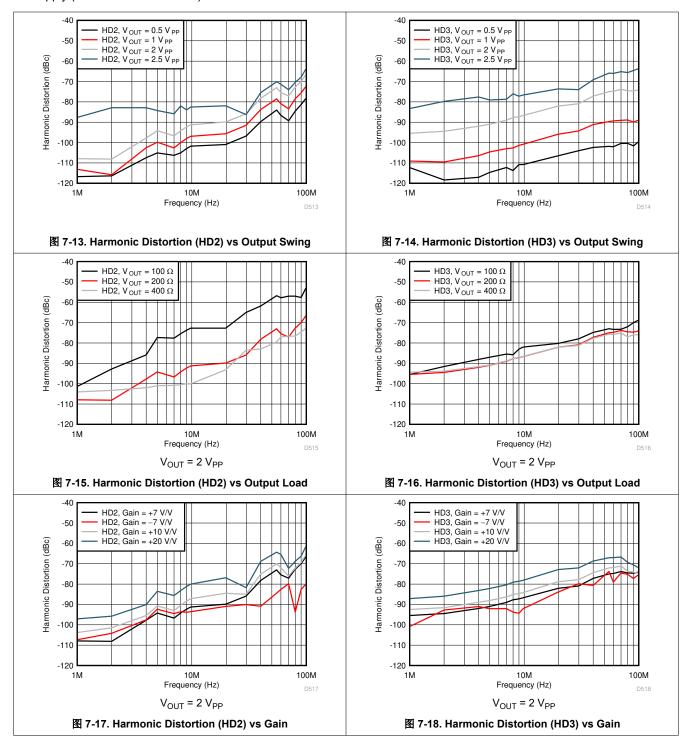

| HD2                         | Second-order harmonic distortion | f = 10 MHz, V <sub>OUT</sub> = 2 V <sub>PP</sub>                                   |        | 90     |     | dBc      |

| пиг                         | Second-order Harmonic distortion | f = 100 MHz, V <sub>OUT</sub> = 2 V <sub>PP</sub>                                  |        | 65     |     | ubc      |

| HD3                         | Third-order harmonic distortion  | f = 10 MHz, V <sub>OUT</sub> = 2 V <sub>PP</sub>                                   |        | 86     |     | dBc      |

| прз                         | Third-order narmonic distortion  | f = 100 MHz, V <sub>OUT</sub> = 2 V <sub>PP</sub>                                  |        | 74     |     | ubc      |

| e <sub>n</sub>              | Input-referred voltage noise     | f = 1 MHz                                                                          |        | 0.98   |     | nV/ √ Hz |

| e <sub>i</sub>              | Input-referred current noise     | f = 1 MHz                                                                          |        | 2.5    |     | pA/ √ Hz |

| z <sub>O</sub>              | Closed-loop output impedance     | f = 1 MHz                                                                          |        | 0.15   |     | Ω        |

| DC PERFO                    | DRMANCE                          |                                                                                    | 1      |        |     |          |

| A <sub>OL</sub>             | Open-loop voltage gain           |                                                                                    | 70     | 76     |     | dB       |

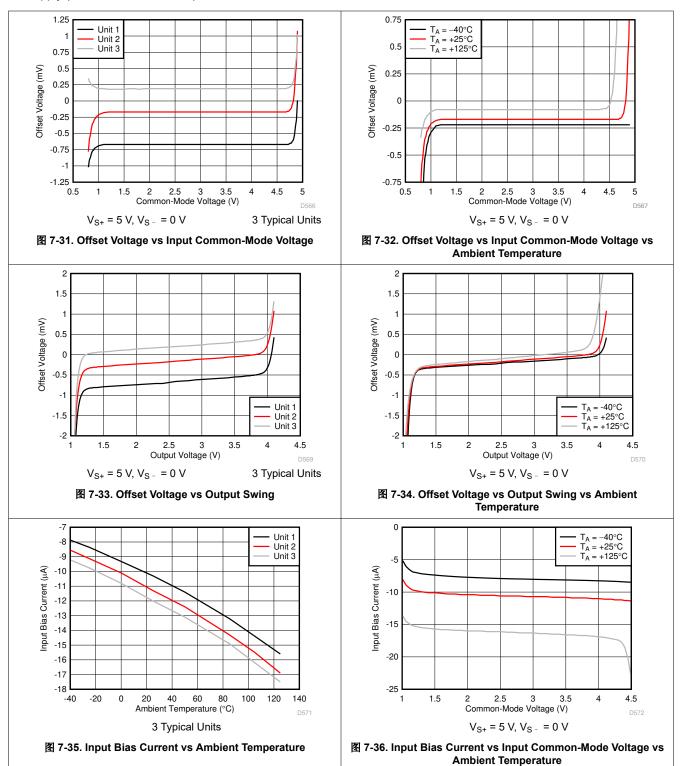

| V <sub>OS</sub>             | Input offset voltage             | T <sub>A</sub> = 25°C                                                              | - 1.5  | ±0.2   | 1.5 | mV       |

| Δ V <sub>OS</sub> / Δ T     | Input offset voltage drift       | $T_A = -40^{\circ}C \text{ to } 125^{\circ}C$                                      |        | 0.5    |     | μV/°C    |

| I <sub>B</sub>              | Input bias current (1)           | T <sub>A</sub> = 25°C                                                              | - 18.5 | - 12   | - 5 | μA       |

| Δ I <sub>B</sub> / Δ T      | Input bias current drift         | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$                               |        | - 0.08 |     | μΑ/°C    |

| I <sub>BOS</sub>            | Input offset current             | T <sub>A</sub> = 25°C                                                              | - 1    | ±0.1   | 1   | μA       |

| Δ I <sub>BOS</sub> /<br>Δ T | Input offset current drift       | T <sub>A</sub> = -40°C to +125°C                                                   |        | 1      |     | nA/°C    |

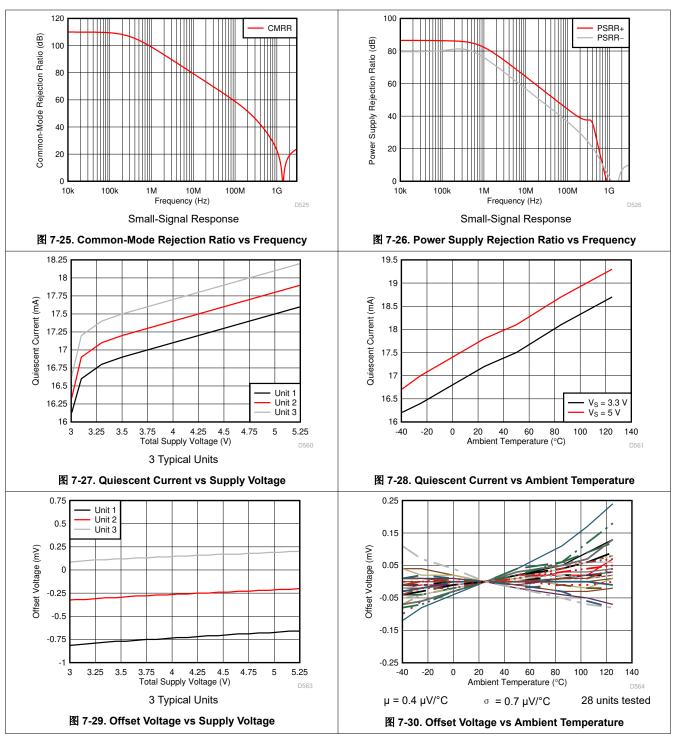

| CMRR                        | Common-mode rejection ratio      | V <sub>CM</sub> = ±0.5 V referred to midsupply                                     | 90     | 100    |     | dB       |

| INPUT                       |                                  |                                                                                    |        |        |     |          |

|                             | Common-mode input resistance     |                                                                                    |        | 2.3    |     | ΜΩ       |

| C <sub>CM</sub>             | Common-mode input capacitance    |                                                                                    |        | 0.6    |     | pF       |

|                             | Differential input resistance    |                                                                                    |        | 5      |     | kΩ       |

| C <sub>DIFF</sub>           | Differential input capacitance   |                                                                                    |        | 0.2    |     | pF       |

| V <sub>IH</sub>             | Common-mode input range (high)   | CMRR > 80 dB, V <sub>S+</sub> = 3.3 V                                              | 2.7    | 2.9    |     | V        |

| V <sub>IL</sub>             | Common-mode input range (low)    | CMRR > 80 dB, V <sub>S+</sub> = 3.3 V                                              |        | 1.1    | 1.3 | V        |

| V <sub>IH</sub>             | Common-mode input range (high)   | CMRR > 80 dB                                                                       | 4.4    | 4.6    |     | V        |

| V <sub>IH</sub>             | Common-mode input range (high)   | $T_A = -40$ °C to +125 °C, CMRR > 80 dB                                            |        | 4.3    |     | V        |

| V <sub>IL</sub>             | Common-mode input range (low)    | CMRR > 80 dB                                                                       |        | 1.1    | 1.3 | V        |

| V <sub>IL</sub>             | Common-mode input range (low)    | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}, \text{ CMRR} > 80 \text{ dB}$ |        | 1.3    |     | V        |

|                             | ·F · · · · · · · · ·             | 7                                                                                  |        |        |     |          |

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

### 7.5 Electrical Characteristics (continued)

at  $V_{S+}$  = 5 V,  $V_{S-}$  = 0 V, G = 7 V/V,  $R_F$  = 453  $\Omega$  , input common-mode biased at midsupply,  $R_L$  = 200  $\Omega$  , output load is referenced to midsupply, and  $T_A$  = 25 $^{\circ}$ C (unless otherwise noted)

|                                       | PARAMETER                                | TEST CONDITIONS                                                                                 | MIN  | TYP  | MAX  | UNIT       |

|---------------------------------------|------------------------------------------|-------------------------------------------------------------------------------------------------|------|------|------|------------|

| OUTPUT                                |                                          |                                                                                                 |      |      |      |            |

| V <sub>OH</sub>                       | Output voltage (high) <sup>(2)</sup>     | T <sub>A</sub> = 25°C, V <sub>S+</sub> = 3.3 V                                                  | 2.35 | 2.4  |      | V          |

|                                       | Outrout walks as (birds)(2)              | T <sub>A</sub> = 25°C                                                                           | 3.95 | 4.1  |      | V          |

| V <sub>OH</sub>                       | Output voltage (high) <sup>(2)</sup>     | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$                                            |      | 4    |      | V          |

| V <sub>OL</sub>                       | Output voltage (low) <sup>(2)</sup>      | T <sub>A</sub> = 25°C, V <sub>S+</sub> = 3.3 V                                                  |      | 1.05 | 1.15 | V          |

| · · · · · · · · · · · · · · · · · · · | Outrot valle as (law)(2)                 | T <sub>A</sub> = 25°C                                                                           |      | 1.05 | 1.15 |            |

| V <sub>OL</sub>                       | Output voltage (low) <sup>(2)</sup>      | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$                                            |      | 1.1  | 1    | V          |

|                                       | Linear submitted drive (sink and source) | $R_L = 10 \Omega, A_{OL} > 60 dB$                                                               | 65   | 80   |      | Л          |

| I <sub>O_LIN</sub>                    | Linear output drive (sink and source)    | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}, R_L = 10 \ \Omega, A_{OL} > 60 \text{ dB}$ |      | 70   |      | mA         |

| I <sub>SC</sub>                       | Output short-circuit current             |                                                                                                 | 85   | 105  |      | mA         |

| POWER                                 | SUPPLY                                   | ,                                                                                               |      |      |      |            |

|                                       | Quiescent current                        |                                                                                                 | 16   | 17.8 | 19.5 |            |

| $I_Q$                                 |                                          | T <sub>A</sub> = -40°C                                                                          |      | 16.7 |      | mA         |

|                                       |                                          | T <sub>A</sub> = 125°C                                                                          |      | 19.5 |      |            |

| PSRR+                                 | Positive power-supply rejection ratio    |                                                                                                 | 80   | 86   |      | dB         |

| PSRR -                                | Negative power-supply rejection ratio    |                                                                                                 | 70   | 80   |      | ав         |

| POWER                                 | DOWN                                     | 1                                                                                               |      |      |      |            |

|                                       | Disable voltage threshold                | Amplifier OFF below this voltage                                                                | 0.65 | 1    |      | V          |

|                                       | Enable voltage threshold                 | Amplifier ON below this voltage                                                                 |      | 1.5  | 1.8  | V          |

|                                       | Power-down quiescent current             |                                                                                                 |      | 70   | 140  | μА         |

|                                       | PD bias current                          |                                                                                                 |      | 70   | 140  | μ <b>А</b> |

|                                       | Turnon time delay                        | Time to V <sub>OUT</sub> = 90% of final value                                                   |      | 15   |      | ns         |

|                                       | Turnoff time delay                       |                                                                                                 |      | 120  |      | ns         |

<sup>(1)</sup> Current flowing into the input pin is considered negative

<sup>(2)</sup> Amplifier output saturated

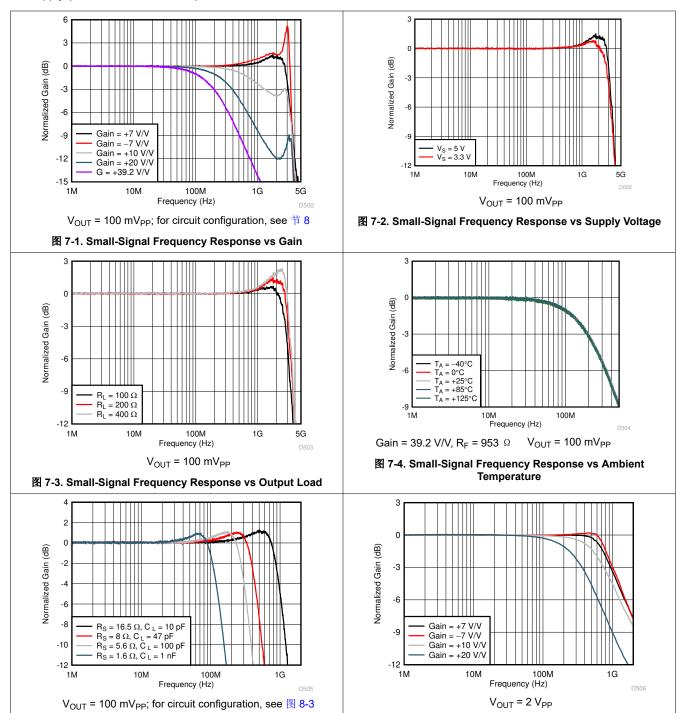

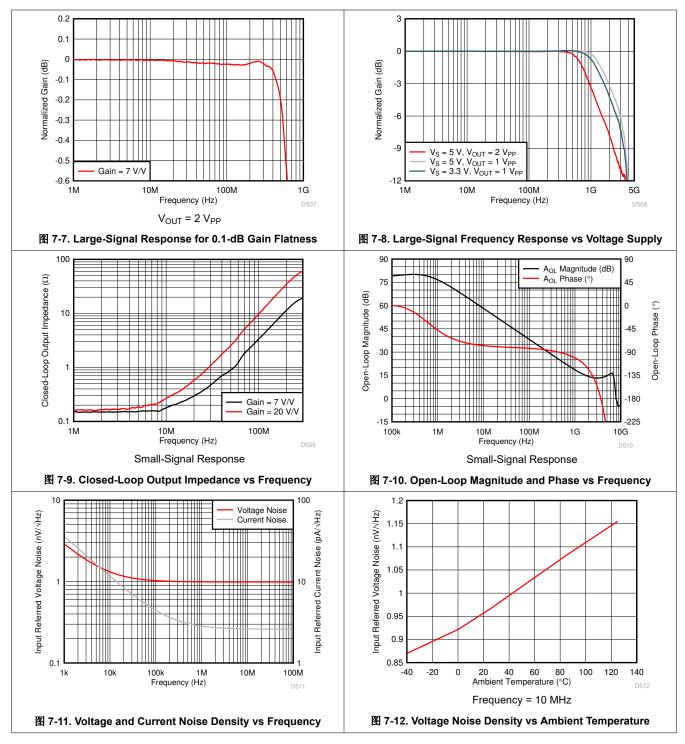

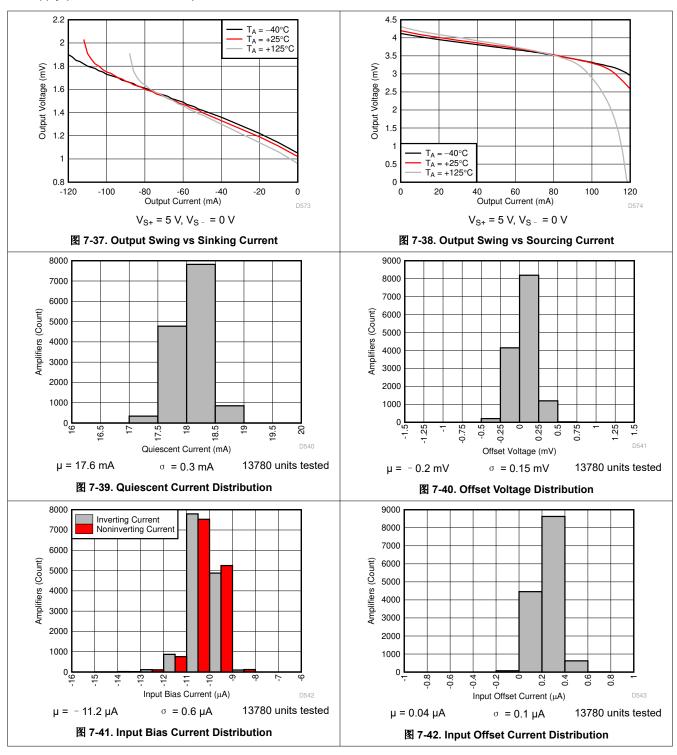

### 7.6 Typical Characteristics

at  $T_A$  = 25°C,  $V_{S+}$  = 2.5 V,  $V_{S-}$  = - 2.5 V,  $V_{IN+}$  = 0 V,  $R_F$  = 453  $\Omega$ , Gain = 7 V/V,  $R_L$  = 200  $\Omega$ , and output load referenced to midsupply (unless otherwise noted)

图 7-5. Small-Signal Frequency Response vs Capacitive Load

图 7-6. Large-Signal Frequency Response vs Gain

at  $T_A$  = 25°C,  $V_{S+}$  = 2.5 V,  $V_{S-}$  = - 2.5 V,  $V_{IN+}$  = 0 V,  $R_F$  = 453  $\Omega$ , Gain = 7 V/V,  $R_L$  = 200  $\Omega$ , and output load referenced to midsupply (unless otherwise noted)

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

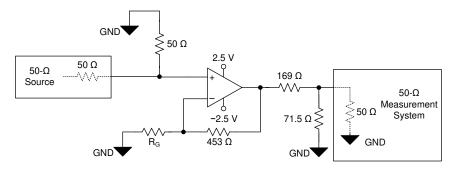

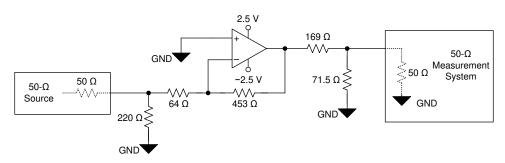

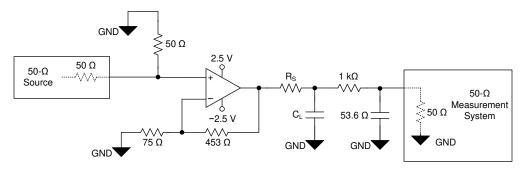

### **8 Parameter Measurement Information**

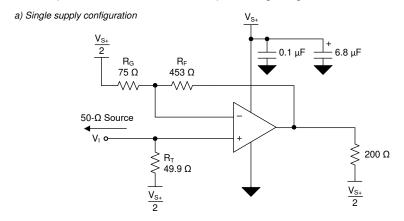

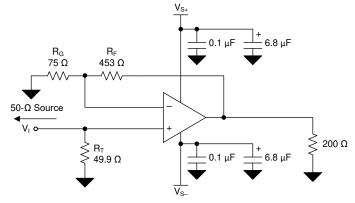

The various test setup configurations for the OPA855 are shown in  $\boxtimes$  8-1,  $\boxtimes$  8-2, and  $\boxtimes$  8-3. When configuring the OPA855 in a gain of +39.2 V/V, feedback resistor R<sub>F</sub> was set to 953  $\Omega$ .

R<sub>G</sub> values depend on gain configuration

图 8-1. Noninverting Configuration

图 8-2. Inverting Configuration (Gain = -7 V/V)

图 8-3. Capacitive Load Driver Configuration

### 9 Detailed Description

#### 9.1 Overview

The ultra-wide, 8-GHz gain bandwidth product (GBWP) of the OPA855, combined with the broadband voltage noise of 0.98 nV/  $\sqrt{\text{Hz}}$ , produces a viable amplifier for wideband transimpedance applications, high-speed data acquisition systems, and applications with weak signal inputs that require low-noise and high-gain front ends. The OPA855 combines multiple features to optimize dynamic performance. In addition to the wide, small-signal bandwidth, the OPA855 has 850 MHz of large-signal bandwidth (2  $V_{PP}$ ), and a slew rate of 2750  $V/\mu s$ , making the device a viable option for high-speed pulsed applications.

### 9.2 Functional Block Diagram

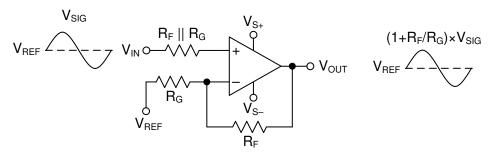

The OPA855 is a classic voltage feedback operational amplifier (op amp) with two high-impedance inputs and a low-impedance output. Standard application circuits are supported, like the two basic options shown in  $\[ \]$  9-1 and  $\[ \]$  9-2. The resistor on the noninverting pin is used for bias current cancellation to minimize the output offset voltage. In a noninverting configuration the additional resistors on the noninverting pin add noise to the system so if SNR is critical, the resistor can be eliminated. In an inverting configuration the noninverting node is typically connected to a DC voltage, so the high-frequency noise contribution from the bias cancellation resistor can be bypassed by adding a large 1- $\mu$ F capacitor in parallel to the resistor to shunt the noise. The DC operating point for each configuration is level-shifted by the reference voltage ( $V_{REF}$ ), which is typically set to midsupply in single-supply operation.  $V_{REF}$  is typically connected to ground in split-supply applications.

图 9-1. Noninverting Amplifier

$$V_{SIG} V_{REF} \circ V_{SH} \circ V$$

图 9-2. Inverting Amplifier

### 9.3 Feature Description

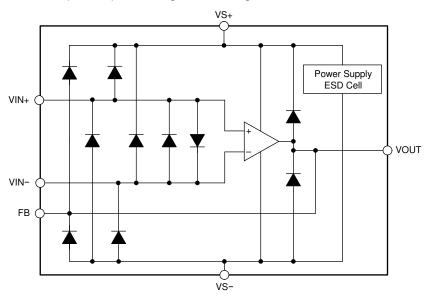

#### 9.3.1 Input and ESD Protection

The OPA855 is fabricated on a low-voltage, high-speed, BiCMOS process. The internal, junction breakdown voltages are low for these small geometry devices, and as a result, all device pins are protected with internal ESD protection diodes to the power supplies as 89-3 shows. There are two antiparallel diodes between the inputs of the amplifier that clamp the inputs during an overrange or fault condition.

图 9-3. Internal ESD Structure

#### 9.3.2 Feedback Pin

The OPA855 pin layout is optimized to minimize parasitic inductance and capacitance, which is a critical care about in high-speed analog design. The FB pin (pin 1) is internally connected to the output of the amplifier. The FB pin is separated from the inverting input of the amplifier (pin 3) by a no connect (NC) pin (pin 2). The NC pin must be left floating. There are two advantages to this pin layout:

- 1. A feedback resistor (R<sub>F</sub>) can connect between the FB and IN pin on the same side of the package (see § 9-4) rather than going around the package.

- 2. The isolation created by the NC pin minimizes the capacitive coupling between the FB and IN pins by increasing the physical separation between the pins.

图 9-4. R<sub>F</sub> Connection Between FB and IN - Pins

#### 9.3.3 Wide Gain-Bandwidth Product

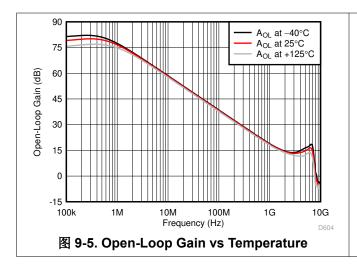

$\[ \]$  7-10 shows the open-loop magnitude and phase response of the OPA855. Calculate the gain bandwidth product of any op amp by determining the frequency at which the  $A_{OL}$  is 40 dB and multiplying that frequency by a factor of 100. The open-loop response shows the OPA855 to have approximately 62° of phase-margin in a noise gain of 7 V/V. The second pole in the  $A_{OL}$  response occurs before the magnitude crosses 0 dB, and the resultant phase margin is less than 0°. This indicates instability at a gain of 0 dB (1 V/V). Amplifiers that are not unity-gain stable are known as decompensated amplifiers. Decompensated amplifiers typically have higher gain-bandwidth product, higher slew rate, and lower voltage noise, compared to a unity-gain stable amplifier with the same amount of quiescent power consumption.

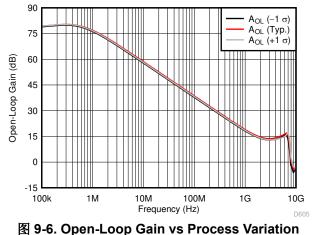

$\ensuremath{\mathbb{R}}$  9-5 shows the open-loop magnitude ( $A_{OL}$ ) of the OPA855 as a function of temperature. The results show approximately 5° of phase-margin variation over the entire temperature range in a noise gain of 7 V/V. Semiconductor process variation is the naturally occurring variation in the attributes of a transistor (Early-voltage,  $\beta$ , channel-length and width) and other passive elements (resistors and capacitors) when fabricated into an integrated circuit. The process variation can occur across devices on a single wafer or across devices over multiple wafer lots over time. Typically, the variation across a single wafer is tightly controlled.  $\ensuremath{\mathbb{R}}$  9-6 shows the  $A_{OL}$  magnitude of the OPA855 as a function of process variation over time. The results show the  $A_{OL}$  curve for the nominal process corner and the variation one standard deviation from the nominal. The simulated results show less than 2° of phase-margin difference within a standard deviation of process variation in a noise gain of 7 V/V.

One of the primary applications for the OPA855 is as a high-speed transimpedance amplifier (TIA). The low-frequency noise gain of a TIA is 0 dB (1 V/V). At high frequencies the ratio of the total input capacitance and the feedback capacitance set the noise gain. To maximize the TIA closed-loop bandwidth, the feedback capacitance is typically smaller than the input capacitance, which implies that the high-frequency noise gain is greater than 0 dB. As a result, op amps configured as TIAs are not required to be unity-gain stable, which makes a decompensated amplifier a viable option for a TIA. What You Need To Know About Transimpedance Amplifiers – Part 1 and What You Need To Know About Transimpedance Amplifiers – Part 2 describe transimpedance amplifier compensation in greater detail.

#### 9.3.4 Slew Rate and Output Stage

In addition to wide bandwidth, the OPA855 features a high slew rate of 2750 V/µs. The slew rate is a critical parameter in high-speed pulse applications with narrow sub-10-ns pulses, such as optical time-domain reflectometry (OTDR) and LIDAR. The high slew rate of the OPA855 implies that the device accurately reproduces a 2-V, sub-ns pulse edge, as seen in  $\boxed{8}$  7-20. The wide bandwidth and slew rate of the OPA855 make it an excellent amplifier for high-speed signal-chain front ends.

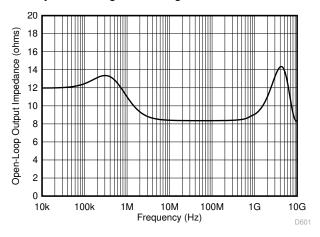

☑ 9-7 shows the open-loop output impedance of the OPA855 as a function of frequency. To achieve high slew rates and low output impedance across frequency, the output swing of the OPA855 is limited to approximately 3 V. The OPA855 is typically used in conjunction with high-speed pipeline ADCs and flash ADCs that have limited input ranges. Therefore, the OPA855 output swing range coupled with the class-leading voltage noise specification maximizes the overall dynamic range of the signal chain.

图 9-7. Open-Loop Output Impedance (Z<sub>OL</sub>) vs Frequency

#### 9.4 Device Functional Modes

#### 9.4.1 Split-Supply and Single-Supply Operation

The OPA855 can be configured with single-sided supplies or split-supplies as shown in [8] 10-11. Split-supply operation using balanced supplies with the input common-mode set to ground eases lab testing because most signal generators, network analyzers, spectrum analyzers, and other lab equipment typically reference inputs and outputs to ground. In split-supply operation, the thermal pad must be connected to the negative supply.

Newer systems use a single power supply to improve efficiency and reduce the cost of the extra power supply. The OPA855 can be used with a single positive supply (negative supply at ground) with no change in performance if the input common-mode and output swing are biased within the linear operation of the device. In single-supply operation, level shift the DC input and output reference voltages by half the difference between the power supply rails. This configuration maintains the input common-mode and output load reference at midsupply. To eliminate gain errors, the source driving the reference input common-mode voltage must have low output impedance across the frequency range of interest. In this case, the thermal pad must be connected to ground.

#### 9.4.2 Power-Down Mode

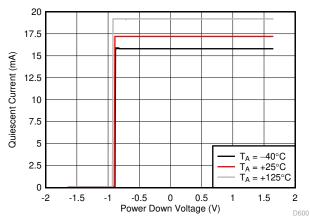

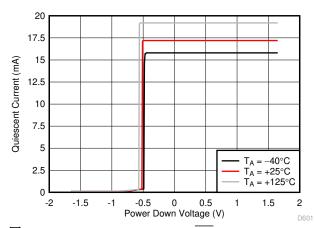

The OPA855 features a power-down mode to reduce the quiescent current to conserve power. ☒ 7-23 and ☒ 7-24 show the transient response of the OPA855 as the PD pin toggles between the disabled and enabled states.

The  $\overline{PD}$  disable and enable threshold voltages are with reference to the negative supply. If the amplifier is configured with the positive supply at 3.3 V and the negative supply at ground, then the disable and enable threshold voltages are 0.65 V and 1.8 V, respectively. If the amplifier is configured with  $\pm 1.65$  V supplies, then the threshold voltages are at -1 V and 0.15 V. If the amplifier is configured with  $\pm 2.5$  V supplies, then the threshold voltages are at -1.85 V and -0.7 V.

图 9-8. Switching Threshold (PD Pin Swept from High to Low)

图 9-9. Switching Threshold (PD Pin Swept from Low to High)

Connecting the  $\overline{PD}$  pin low disables the amplifier and places the output in a high-impedance state. When the amplifier is configured as a noninverting amplifier, the feedback (R<sub>F</sub>) and gain (R<sub>G</sub>) resistor network form a parallel load to the output of the amplifier. To protect the input stage of the amplifier, the OPA855 uses internal, back-to-back protection diodes between the inverting and noninverting input pins as  $\boxed{\$}$  9-3 shows. In the power-down state, if the differential voltage between the input pins of the amplifier exceeds a diode voltage drop, an additional low-impedance path is created between the noninverting input pin and the output pin.

### 10 Application, Implementation, and Layout

#### 备注

以下应用部分中的信息不属于 TI 器件规格的范围, TI 不担保其准确性和完整性。TI 的客户应负责确定器件是否适用于其应用。客户应验证并测试其设计,以确保系统功能。

### 10.1 Application Information

The OPA855 offers very high-bandwidth, high slew-rate, low noise, and better than - 60 dBc of distortion performance at frequencies of up to 100 MHz. These features make this device an excellent low-noise amplifier in high-speed data acquisition systems.

#### 10.2 Typical Application

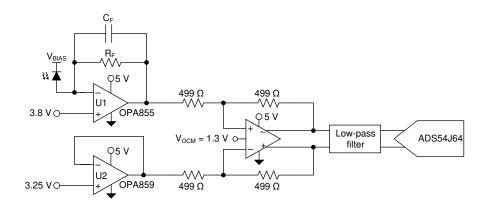

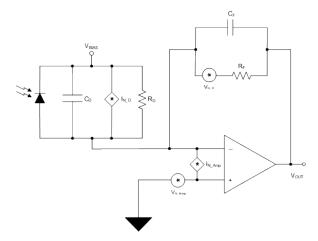

☑ 10-1 shows the OPA855 configured as a transimpedance amplifier (U1) in a wide-bandwidth, optical front-end system. A second amplifier, the OPA859-Q1, configured as a unity-gain buffer (U2) sets a dc offset voltage to the THS4520. The THS4520 is used to convert the single-ended transimpedance output of the OPA855 into a differential output signal. The THS4520 drives the input of the ADS54J64, 14-bit, 1-GSPS analog-to-digital converter (ADC) that digitizes the analog signal.

图 10-1. OPA855 as a TIA in an Optical Front-End System

#### 10.2.1 Design Requirements

The objective is to design a low noise, wideband optical front-end system using the OPA855 as a transimpedance amplifier. The design requirements are:

- Amplifier supply voltage: 5 VTIA common-mode voltage: 3.8 V

- THS4520 gain: 1 V/V

- ADC input common-mode voltage: 1.3 V

ADC analog differential input range: 1.1 V<sub>PP</sub>

#### 10.2.2 Detailed Design Procedure

The closed-loop bandwidth of a transimpedance amplifier is a function of the following:

- 1. The total input capacitance (C<sub>IN</sub>). This total includes the photodiode capacitance, the input capacitance of the amplifier (common-mode and differential capacitance) and any stray capacitance from the PCB.

- 2. The op amp gain bandwidth product (GBWP).

- 3. The transimpedance gain  $(R_F)$ .

Copyright © 2023 Texas Instruments Incorporated

Submit Document Feedback

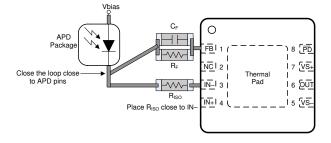

$\[ \]$  10-1 shows the OPA855 configured as a TIA, with the avalanche photodiode (APD) reverse biased so that the APD cathode is tied to a large positive bias voltage. In this configuration, the APD sources current into the op amp feedback loop so that the output swings in a negative direction relative to the input common-mode voltage. To maximize the output swing in the negative direction, the OPA855 common-mode voltage is set close to the positive limit; only 1.2 V from the positive supply rail. The feedback resistance ( $R_F$ ) and the input capacitance ( $C_{IN}$ ) form a zero in the noise gain that results in instability if left unchecked. To counteract the effect of the zero, a pole is inserted into the noise gain transfer function by adding the feedback capacitor ( $C_F$ ).

The *Transimpedance Considerations for High-Speed Amplifiers Application Report* discusses theories and equations that show how to compensate a transimpedance amplifier for a particular transimpedance gain and input capacitance. The bandwidth and compensation equations from the application report are available in an Excel® calculator. *What You Need To Know About Transimpedance Amplifiers* – *Part 1* provides a link to the calculator.

The equations and calculators in the referenced application report and blog posts are used to model the bandwidth ( $f_{-3dB}$ ) and noise ( $I_{RN}$ ) performance of the OPA855 configured as a TIA. The resultant performance is shown in  $\[mu]$  10-2 and  $\[mu]$  10-3. The left-side Y-axis shows the closed-loop bandwidth performance, whereas the right side of the graph shows the integrated input-referred noise. The noise bandwidth to calculate  $I_{RN}$  for a fixed  $R_F$  and  $C_{PD}$  is set equal to the  $f_{-3dB}$  frequency.  $\[mu]$  10-2 shows the amplifier performance as a function of photodiode capacitance ( $C_{PD}$ ) for  $R_F = 6$  k $\Omega$  and 12 k $\Omega$ . Increasing  $C_{PD}$  decreases the closed-loop bandwidth. To maximize bandwidth, make sure to reduce any stray parasitic capacitance from the PCB. The OPA855 is designed with 0.8 pF of total input capacitance to minimize the effect of stray capacitance on system performance.  $\[mu]$  10-3 shows the amplifier performance as a function of  $R_F$  for  $C_{PD} = 1.5$  pF and 2.5 pF. Increasing  $R_F$  results in lower bandwidth. To maximize the signal-to-noise ratio (SNR) in an optical front-end system, maximize the gain in the TIA stage. Increasing  $R_F$  by a factor of X increases the signal level by X, but only increases the resistor noise contribution by  $\sqrt{X}$ , thereby improving SNR. Since the OPA855 is a bipolar input amplifier, increasing the feedback resistance increases the voltage offset due to the bias current and also increases the total output noise due to increased noise contributions from the amplifiers current noise.

The OPA859-Q1 configured as a unity-gain buffer drives a DC offset voltage of 3.25 V into the lower half of the THS4520. To maximize the dynamic range of the ADC, the OPA855-Q1 and OPA859-Q1 drive a differential common-mode of 3.8 V and 3.25 V respectively into the THS4520. The dc offset voltage of the buffer amplifier can be derived using 方程式 1.

$$V_{BUF\_DC} = V_{TIA\_CM} - \left(\frac{1}{2} \times \frac{V_{ADC\_DIFF\_IN}}{\left(\frac{R_F}{R_G}\right)}\right)$$

(1)

#### where

- V<sub>TIA CM</sub> is the common-mode voltage of the TIA (3.8 V)

- $V_{ADC\ DIFF\ IN}$  is the differential input voltage range of the ADC (1.1  $V_{PP}$ )

- R<sub>F</sub> and R<sub>G</sub> are the feedback resistance (499  $\,^{\Omega}$ ) and gain resistance (499  $\,^{\Omega}$ ) of the THS4520 differential amplifier

The low-pass filter between the THS4520 and the ADC54J64 minimizes high-frequency noise and maximizes SNR. The ADC54J64 has an internal buffer that isolates the output of the THS4520 from the ADC sampling-capacitor input, so a traditional charge bucket filter is not required.

### 10.2.3 Application Curves

### 10.3 Typical Application

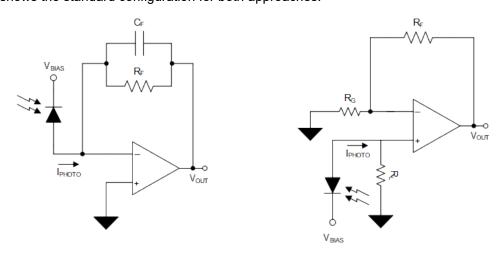

There are two main approaches for current to voltage conversion. One uses a non-inverting voltage feedback amplifier in combination with a shunt resistor to first convert current and then further amplify the optical signal. The other approach configures an amplifier for transimpedance applications which combines both steps into one. \$\mathbb{\exist}\$ 10-4 shows the standard configuration for both approaches.

图 10-4. Transimpedance Amplifier vs. Voltage Feedback Amplifier

Both configurations provide a low output impedance stage which provides the ability to interface with various types of loads. However, the non-inverting option comes with a few disadvantages. TIA's input impedance is near zero, since the amplifier keeps the voltage at the inverting input node at the same potential as the non-inverting input node. While the VFB's input impedance is equal to the shunt resistor  $R_L$ . In the case of the VFB amplifier, the signal response will be slowed due to a large time constant created by the shunt resistor and capacitor. Also, the linearity of the photodetector can suffer, especially for higher detector currents due to the varying voltage bias produced at the shunt resistor. And, since the voltage bias of the photodetector is no longer constant for all detector currents, the diode's internal capacitance will vary. Using a TIA, the voltage bias remains constant at the voltage set by the non-inverting node, and can provide level shifting to the signal which is especially useful for single-supply configurations.

OPA855 offers 8 GHz of gain bandwidth, high slew-rate, and low noise which makes this device suitable for a wide range of photodetectors.

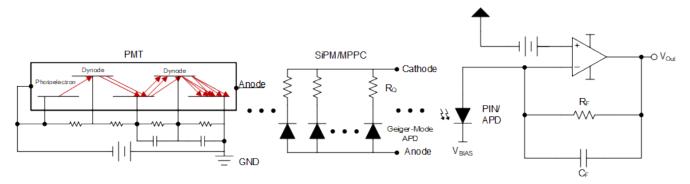

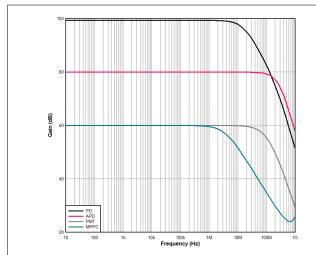

10-5 shows the OPA855 configured as a transimpedance amplifier (TIA) in a wide-bandwidth, optical front-end system. Various types of optical sensors can be used as an optical input to the amplifier: photodiode (PD), avalanche photodiode (APD), Photomultiplier Tube (PMT), and Multi-Pixel Photon Counter (MPPC) or known as Solid-State Photomultiplier (SiPM). Optical detection applications have commonly used APDs, but ultra-low light source detection has been a challenge in past solutions. With technologies such as PMTs and MPPCs, their high intrinsic gain, while maintaining a fast output, requires a low noise, high-speed interface. The OPA855 can accommodate for these optical challenges and would work equally as well in these applications.

图 10-5. Transimpedance Amplifier with APD or SiPM/MPPC or PMT Inputs

Transimpedance applications require low voltage and current noise for optimal system performance. Due to its high input impedance structure, the OPA855 has a great balance between low input-referred voltage noise and current noise which is consistent over frequency. Overall, the amplifier noise should have minimal impact to the total noise of the application. We would need to examine the total input referred noise to the optical sensor.

Noise sources in optical sensors vary especially when introducing gain and photon paralleling. Optical power, gain, and applied reverse bias are the main characteristics that will affect signal to noise ratio. Standard photodiodes contribute the lowest noise at the highest quantum efficiency. Internal to photodiodes, noises sources include shot and thermal. Shot noise is a random occurrence of photodetection which arises in periods of both light and dark. Dark current is noise that occurs in the absence of an optical source which can be included with shot noise. And, thermal noise originates from the shunt resistance internal to the diode. At the lower signal levels, shot noise will dominate. 10-6 shows an example of the noise sources present in a transimpedance amplifier circuit. The total TIA noise is the root sum square of each component within the system: photodiode noise, amplifier current noise, amplifier voltage noise, and feedback resistor noise.

图 10-6. Photodiode and TIA Noise Model

Interfacing with APDs is similar to interfacing with PIN PDs, but APDs have additional noise factors due to its internal gain. APDs have increased shot noise and the addition of a multiplication excess noise factor. Decreasing capacitance, increasing diode shunt resistance, and decreasing reverse voltage bias applied to the APD deceases noise at the expense of response time. MPPCs' total noise is comparable to APDs, but with differing noise sources. This optical sensor includes digital-like noise factors such as dark count rate, after pulsing, and optical crosstalk due to its paralleling gain cells. For PMTs, dark count rate is lower. In general, PMTs' total noise is comparable to PDs' with an internal gain comparable to APDs'. However, PMTs have the lowest quantum efficiency of the optical sensor space.

#### 10.3.1 Design Requirements

The objective is to design a low noise, wideband optical front-end system using a diverse selection of optical sensors: PD, APD, PMT, and MPPC with the OPA855 as the TIA. The approximate design requirements for each type of photodetector are listed in  $\frac{10}{5}$  10-1.

|             | ₹ 10 1. Design Farameters |                  |                           |                           |                                    |                              |  |  |  |  |  |  |

|-------------|---------------------------|------------------|---------------------------|---------------------------|------------------------------------|------------------------------|--|--|--|--|--|--|

| Sensor      | Intrinsic Gain<br>(A/W)   | Reverse Bias (V) | Input<br>Capacitance (pF) | Target<br>Bandwidth (MHz) | Transimpedance Gain $R_F(k\Omega)$ | Total Optical<br>Gain (kV/W) |  |  |  |  |  |  |

| PD (PIN)    | 1                         | 30               | 3                         | 15                        | 100                                | 100                          |  |  |  |  |  |  |

| APD         | 100                       | 150              | 1                         | 200                       | 10                                 | 1000                         |  |  |  |  |  |  |

| PMT         | 1×10 <sup>6</sup>         | 1250             | 50                        | 100                       | 1                                  | 1×10 <sup>6</sup>            |  |  |  |  |  |  |

| MPPC (SiPM) | 5×10 <sup>5</sup>         | 50               | 100                       | 10                        | 1                                  | 5×10 <sup>5</sup>            |  |  |  |  |  |  |

表 10-1. Design Parameters

#### 10.3.2 Detailed Design Procedure

The OPA855 is decompensated and requires a high-frequency gain of 7V/V or greater to be stable. Using the OPA855 in lower gains results in increased peaking and potential instability. Decompensated amplifiers are advantageous in TIA applications due the inherent characteristics of a TIA design. The zero and pole pair introduced by the input and feedback capacitances along with the feedback resistor increases the noise gain until it flattens out at a high gain with a magnitude shown in 方程式 2.

$$1 + \frac{c_{TOT}}{c_F} \tag{2}$$

#### where

- C<sub>TOT</sub> is the total input capacitance of the amplifier (includes photodetector capacitance and the common-mode and differential input capacitance of the amplifier)

- · C<sub>F</sub> is the feedback capacitance of the amplifier

A decompensated amplifier allows for benefits such as increased open loop gain, increased bandwidth, increased slew rate, and lower input referred noise for the same quiescent current relative to its unity gain stable counterpart.

Similar to the concept described in  $\dagger$  10.2.2, the rise time and the internal capacitance of the photodetector will determine the closed-loop bandwidth. Both the closed-loop bandwidth and the transimpedance gain (R<sub>F</sub>) determine the necessary gain bandwidth (GBWP) of the amplifier.  $\ddagger$  10-1 shows the standard photodiode characteristics based on type of photodetector. Target values such as the system bandwidth and gain were calculated using these concepts with the chosen photodiode characteristics. Detailed explanations and equations can be found in the application reports discussed in  $\dagger$  10.2.2.

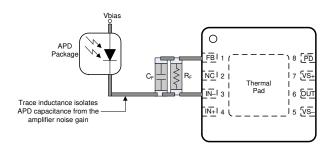

☑ 10-5 shows the OPA855 configured as a TIA, with the optical sensor reverse biased so that the diode cathode is tied to the positive bias voltage. A RC filter can be used at the reverse bias node as a low pass filter to eliminate high frequency noise. The internal capacitance of photodetectors will vary based on sensor type and the value of the applied reverse voltage. The setups between each sensor type will slightly differ, but the connection to the amplifier will be consistent throughout.

Copyright © 2023 Texas Instruments Incorporated

The difference between each optical design comprise choosing the optimal feedback resistor to set the transimpedance gain and the optimal feedback capacitance to compensate for the additional input capacitance. With an 8 GHz GBWP, the OPA855 can accommodate very fast rise times to pair with emerging optical sensors to meet the industry's demands for faster optical detections.

The DC voltage bias at the non-inverting input of the OPA855 shown in <a>\invertigal{\text{N}}\$</a> 10-5 will set the common-mode voltage which will maximize the output swing of the system in mismatched power supply configurations. The DC bias is critical to avoid clipping or saturating the output stage of the amplifier. For the later stages, a fully differential amplifier (FDA) can be used to convert single-ended signal to a differential input to drive an analog-to-digital converter (ADC) as shown in <a>\mathbb{\text{N}}\$</a> 10-1. Higher order filters can be added between the FDA and ADC for system noise reduction.

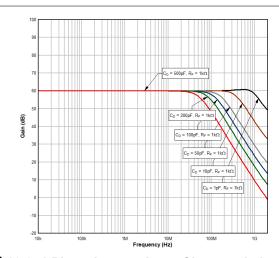

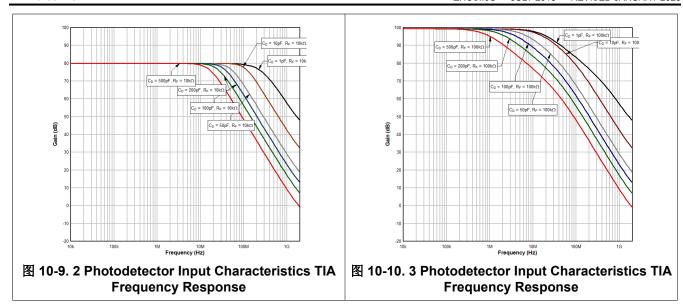

图 10-7 shows the performance that results from the design parameters provided in 表 10-1, and 图 10-8 shows the general trends. Both figures depict the closed-loop bandwidth performance of the OPA855 configured as a TIA using different sensor types and gain configurations. 图 10-7 shows the amplifier performance based on the chosen photodetector from the values provided in 表 10-1. PMTs and MPPCs have higher intrinsic gains, but requires a wide bandwidth to compensate for its higher internal capacitance. Whereas, PDs and APDs require higher gain configurations to achieve similar output voltage levels. The OPA855 is able to provide the bandwidth to accommodate for both optical challenges. 图 10-7 shows a generic view of the amplifier performance as a function of sensor capacitance and transimpedance gain. Increasing the feedback resistance and input capacitance, decreases the closed-loop bandwidth. Throughout the trends, the amount of change in closed-loop bandwidth is consistent in relationship of the changes in both terms. A photodiode capacitance of 1 pF and a feedback resistance of 1 k $\Omega$  results in a very high closed-loop system bandwidth of 1.1 GHz.

### 10.3.3 Application Curves

图 10-7. Optical Sensor TIA Frequency Response

图 10-8. 1 Photodetector Input Characteristics TIA Frequency Response

### 10.4 Power Supply Recommendations

The OPA855 operates on supplies from 3.3 V to 5.25 V. The OPA855 operates on single-sided supplies, split and balanced bipolar supplies, and unbalanced bipolar supplies. Because the OPA855 does not feature rail-to-rail inputs or outputs, the input common-mode and output swing ranges are limited at 3.3-V supplies.

b) Split supply configuration

图 10-11. Split and Single Supply Circuit Configuration

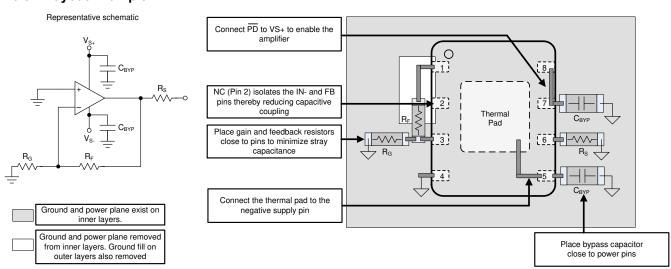

### 10.5 Layout

#### 10.5.1 Layout Guidelines

Achieving optimum performance with a high-frequency amplifier like the OPA855 requires careful attention to board layout parasitics and external component types. Recommendations that optimize performance include:

- Minimize parasitic capacitance from the signal I/O pins to ac ground. Parasitic capacitance on the output and inverting input pins can cause instability. To reduce unwanted capacitance, cut out the power and ground traces under the signal input and output pins. Otherwise, ground and power planes must be unbroken elsewhere on the board. When configuring the amplifier as a TIA, if the required feedback capacitor is less than 0.15 pF, consider using two series resistors, each of half the value of a single resistor in the feedback loop to minimize the parasitic capacitance from the resistor.

- Minimize the distance (less than 0.25-in) from the power-supply pins to high-frequency bypass capacitors. Use high-quality, 100-pF to 0.1-µF, COG and NPO-type decoupling capacitors with voltage ratings at least three times greater than the amplifiers maximum power supplies. This configuration makes sure that there is a low-impedance path to the amplifiers power-supply pins across the amplifiers gain bandwidth specification. At the device pins, do not allow the ground and power plane layout to be in close proximity to the signal I/O pins. Avoid narrow power and ground traces to minimize inductance between the pins and the decoupling capacitors. The power-supply connections must always be decoupled with these capacitors. Larger (2.2-µF to 6.8-µF) decoupling capacitors that are effective at lower frequency must be used on the supply pins. Place these decoupling capacitors further from the device. Share the decoupling capacitors among several devices in the same area of the printed circuit board (PCB).

- Careful selection and placement of external components preserves the high-frequency performance of the OPA855. Use low-reactance resistors. Surface-mount resistors work best and allow a tighter overall layout. Never use wirewound resistors in a high-frequency application. Because the output pin and inverting input pin are the most sensitive to parasitic capacitance, always position the feedback and series output resistor, if any, as close to the output pin as possible. Place other network components (such as noninverting input termination resistors) close to the package. Even with a low parasitic capacitance shunting the external resistors, high resistor values create significant time constants that can degrade performance. When configuring the OPA855 as a voltage amplifier, keep resistor values as low as possible and consistent with load driving considerations. Decreasing the resistor values keeps the resistor noise terms low and minimizes the effect of the parasitic capacitance. However, lower resistor values increase the dynamic power consumption because R<sub>F</sub> and R<sub>G</sub> become part of the output load network of the amplifier.

#### 10.5.2 Layout Example

图 10-12. Layout Recommendation

www.ti.com.cn

The layout shown in

☐ 10-13 can be improved by following some of the guidelines shown in ☐ 10-14. The two key rules to follow are:

- Add an isolation resistor R<sub>ISO</sub> as close as possible to the inverting input of the amplifier. Select the value of R<sub>ISO</sub> to be between 10 Ω and 20 Ω. The resistor dampens the potential resonance caused by the trace inductance and the amplifiers internal capacitance.

- Close the loop between the feedback elements (R<sub>F</sub> and C<sub>F</sub>) and R<sub>ISO</sub> as close to the APD pins as possible.

This ensures a more balanced layout and reduces the inductive isolation between the APD and the feedback network.

Noise Gain =

$$\left(1 + \frac{Z_F}{Z_{IN}}\right)$$

(3)

#### where

- Z<sub>F</sub> is the total impedance of the feedback network.

- Z<sub>IN</sub> is the total impedance of the input network.

图 10-13. Non-Ideal TIA Layout

图 10-14. Improved TIA Layout

### 11 Device and Documentation Support

### 11.1 Device Support

### 11.1.1 Development Support

- · LIDAR Pulsed Time of Flight Reference Design

- LIDAR-Pulsed Time-of-Flight Reference Design Using High-Speed Data Converters

- · Wide Bandwidth Optical Front-end Reference Design

#### 11.2 Documentation Support

#### 11.2.1 Related Documentation

For related documentation, see the following:

- Texas Instruments, OPA855EVM user's guide

- Texas Instruments, Training Video: High-Speed Transimpedance Amplifier Design Flow

- Texas Instruments, Training Video: How to Design Transimpedance Amplifier Circuits

- Texas Instruments, Training Video: How to Convert a TINA-TI Model into a Generic SPICE Model

- Texas Instruments, Transimpedance Considerations for High-Speed Amplifiers application report

- Texas Instruments, What You Need To Know About Transimpedance Amplifiers Part 1

- Texas Instruments What You Need To Know About Transimpedance Amplifiers Part 2

### 11.3 Receiving Notification of Documentation Updates

To receive notification of documentation updates, navigate to the device product folder on ti.com. In the upper right corner, click on *Alert me* to register and receive a weekly digest of any product information that has changed. For change details, review the revision history included in any revised document.

### 11.4 支持资源

TI E2E™ 支持论坛是工程师的重要参考资料,可直接从专家获得快速、经过验证的解答和设计帮助。搜索现有解答或提出自己的问题可获得所需的快速设计帮助。

链接的内容由各个贡献者"按原样"提供。这些内容并不构成 TI 技术规范,并且不一定反映 TI 的观点;请参阅 TI 的《使用条款》。

#### 11.5 Trademarks

TI E2E<sup>™</sup> is a trademark of Texas Instruments.

Excel® is a registered trademark of Microsoft Corporation.

所有商标均为其各自所有者的财产。

#### 11.6 静电放电警告

静电放电 (ESD) 会损坏这个集成电路。德州仪器 (TI) 建议通过适当的预防措施处理所有集成电路。如果不遵守正确的处理和安装程序,可能会损坏集成电路。

ESD 的损坏小至导致微小的性能降级,大至整个器件故障。精密的集成电路可能更容易受到损坏,这是因为非常细微的参数更改都可能会导致器件与其发布的规格不相符。

#### 11.7 术语表

TI术语表本术语表列出并解释了术语、首字母缩略词和定义。

## 12 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

www.ti.com 2-May-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins | Package qty   Carrier | RoHS | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|--------|---------------|----------------|-----------------------|------|-------------------------------|----------------------------|--------------|------------------|

|                       |        |               |                |                       |      | (4)                           | (5)                        |              |                  |

| OPA855IDSGR           | Active | Production    | WSON (DSG)   8 | 3000   LARGE T&R      | Yes  | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | 855              |

| OPA855IDSGT           | Active | Production    | WSON (DSG)   8 | 250   SMALL T&R       | Yes  | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | 855              |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF OPA855:

Automotive : OPA855-Q1

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

# **PACKAGE OPTION ADDENDUM**

www.ti.com 2-May-2025

| NOTE: Qualified Version Definiti | tions | Definit | ersion/ | Qualified 3 | NOTE: |

|----------------------------------|-------|---------|---------|-------------|-------|

|----------------------------------|-------|---------|---------|-------------|-------|

• Automotive - Q100 devices qualified for high-reliability automotive applications targeting zero defects

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 17-Jan-2023

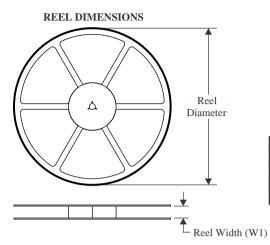

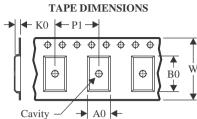

### TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

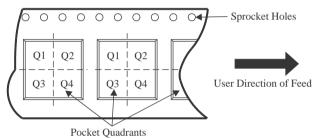

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device      | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| OPA855IDSGR | WSON            | DSG                | 8 | 3000 | 180.0                    | 8.4                      | 2.3        | 2.3        | 1.15       | 4.0        | 8.0       | Q2               |

| OPA855IDSGT | WSON            | DSG                | 8 | 250  | 180.0                    | 8.4                      | 2.3        | 2.3        | 1.15       | 4.0        | 8.0       | Q2               |

# PACKAGE MATERIALS INFORMATION

www.ti.com 17-Jan-2023

### \*All dimensions are nominal

| Device      | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------|--------------|-----------------|------|------|-------------|------------|-------------|

| OPA855IDSGR | WSON         | DSG             | 8    | 3000 | 210.0       | 185.0      | 35.0        |

| OPA855IDSGT | WSON         | DSG             | 8    | 250  | 210.0       | 185.0      | 35.0        |

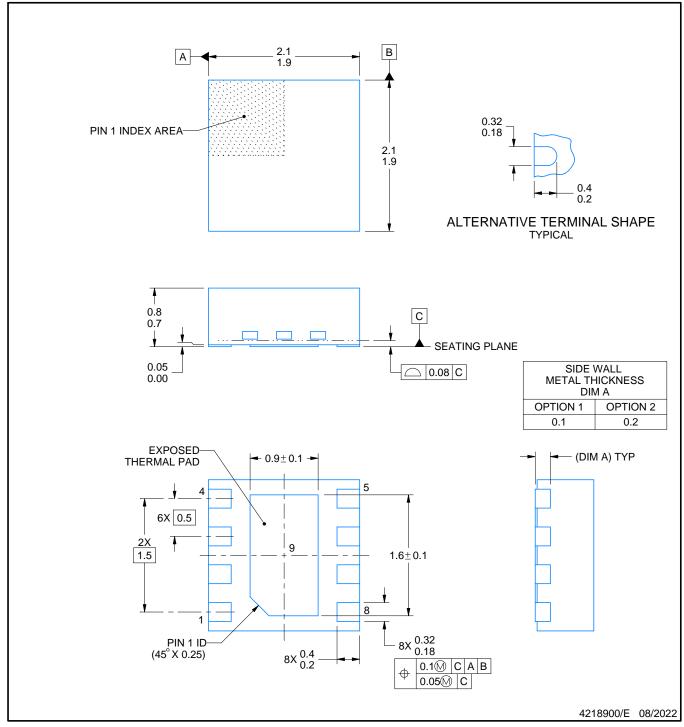

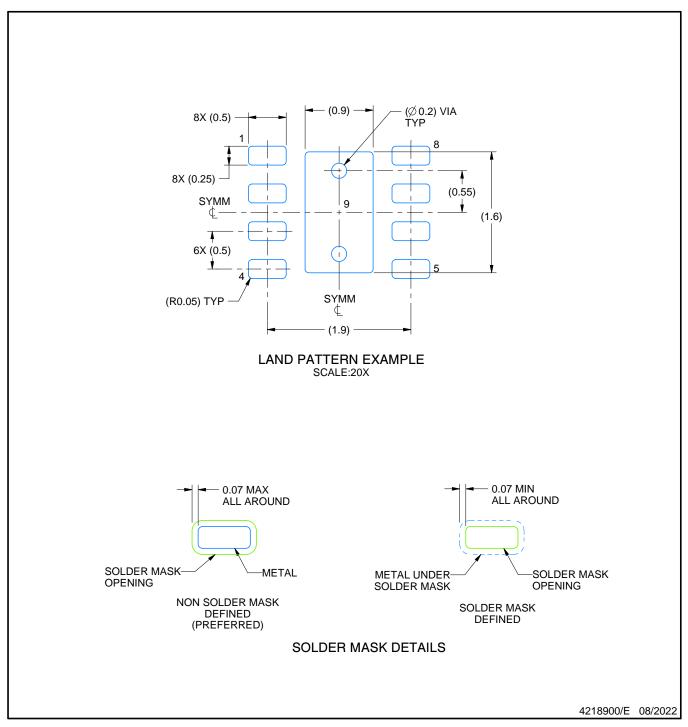

2 x 2, 0.5 mm pitch

PLASTIC SMALL OUTLINE - NO LEAD

This image is a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

PLASTIC SMALL OUTLINE - NO LEAD

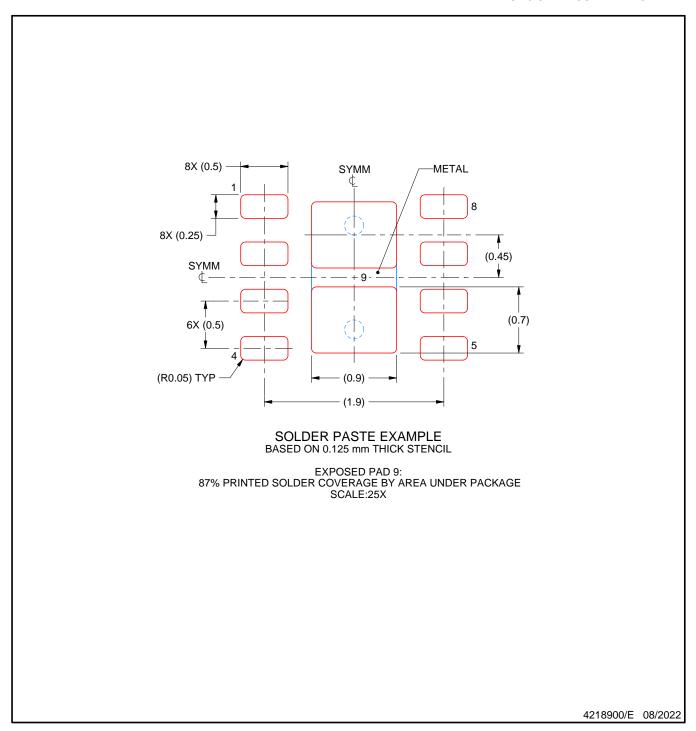

#### NOTES:

- All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

PLASTIC SMALL OUTLINE - NO LEAD

NOTES: (continued)

- 4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

PLASTIC SMALL OUTLINE - NO LEAD

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

### 重要通知和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的相关应用。 严禁以其他方式对这些资源进行复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 版权所有 © 2025,德州仪器 (TI) 公司